Yichao MA, Liangyi WANG, Haiyun TENG, Junguo JIANG. Design of a TDC chip based on 0.18 μm SMIC technology[J]. NUCLEAR TECHNIQUES, 2022, 45(11): 110402

Search by keywords or author

- NUCLEAR TECHNIQUES

- Vol. 45, Issue 11, 110402 (2022)

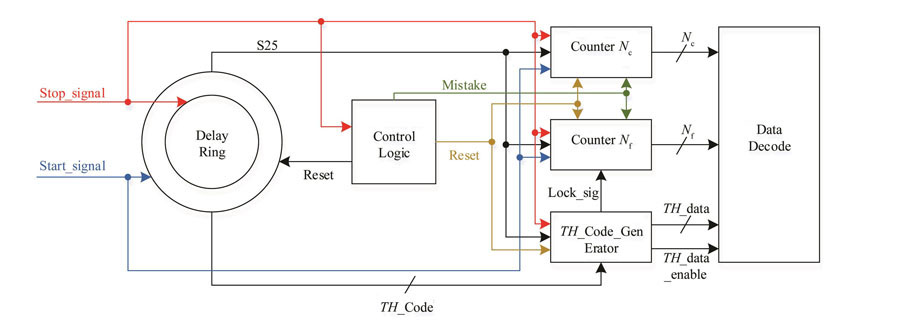

Fig. 1. Diagram of TDC chip structure

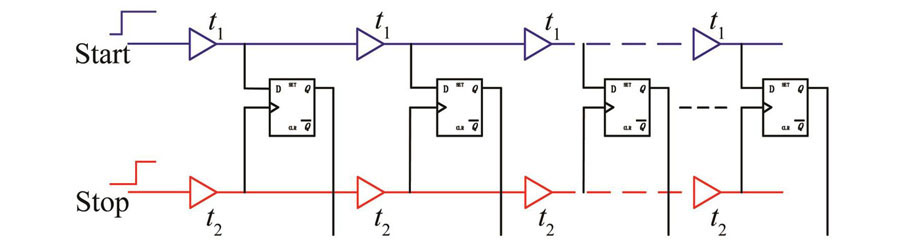

Fig. 2. Differential delay chain TDC

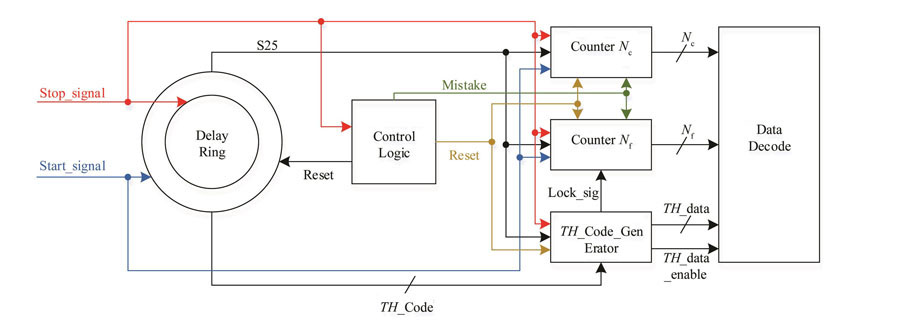

Fig. 3. Differential delay ring TDC

Fig. 4. Diagram of judgment unit combination(a) TDC first loop operation, (b) TDC second loop operation

Fig. 5. Sequence diagram of differential ring TDC

Fig. 6. Structure diagram of arbiter (a) Rise edge arbiter, (b) Falling edge arbiter

Fig. 7. Operating cycle of arbiter A

Fig. 8. Unexpected "01" conversion of arbiter B

Fig. 9. The sequence diagram shows that the register group filters out the false "01" at the falling edge (a) Fake "01" sequence diagram, (b) Sequence diagram after filtering fake "01"

Fig. 10. Sequence diagram of B1 (a) and B2 (b)

Fig. 11. Chip layout

Fig. 12. TDC chip diagram

Fig. 13. Calibration curve of delay ring

Fig. 14. Time accuracy of TDC

Fig. 15. Comparison of local time difference

Fig. 16. Comparison of overall time difference

Fig. 17. Counts of each TDC delay bin

Fig. 18. DNL test results

Fig. 19. INL test results

|

Table 1. Comparison of TDC chips with different designs

Set citation alerts for the article

Please enter your email address