Luyao XIAO, Xi TANG, Xiaodong LIN, Ziye GAO, Zhifei DUAN, Xiaorui DU, Guangqiong XIA, Zhengmao WU, Tao DENG. Reconfigurable Logic Operation Based on Optically Injected VCSEL-SA Subject to Current Modulation[J]. Acta Photonica Sinica, 2022, 51(11): 1114005

Search by keywords or author

- Acta Photonica Sinica

- Vol. 51, Issue 11, 1114005 (2022)

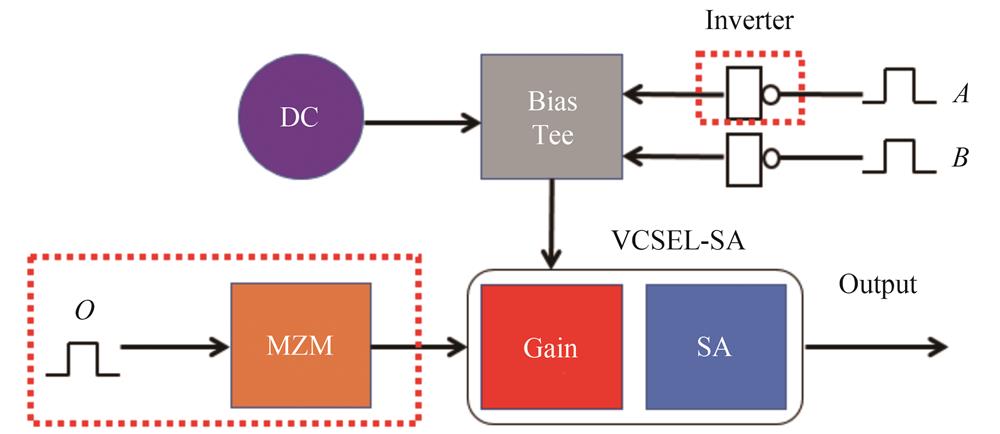

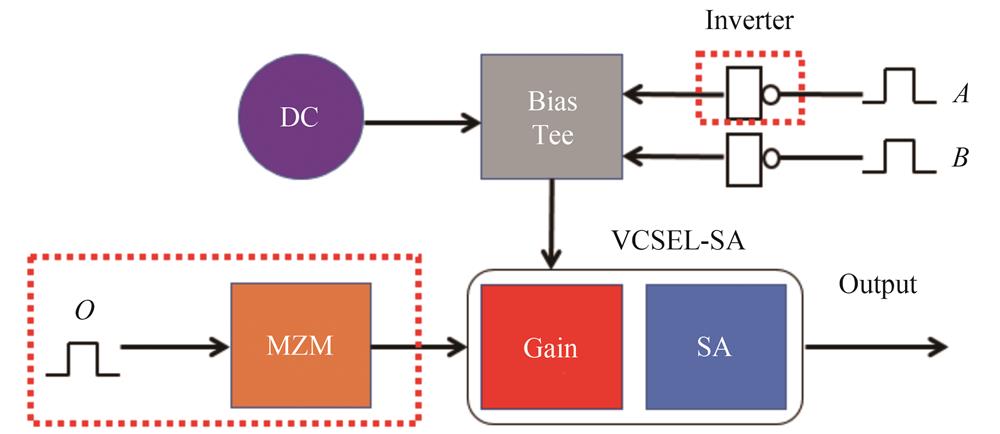

Fig. 1. Schematic diagram of photoelectric logic gate(NOT,NAND,NOR,XOR)based on VCSEL-SA

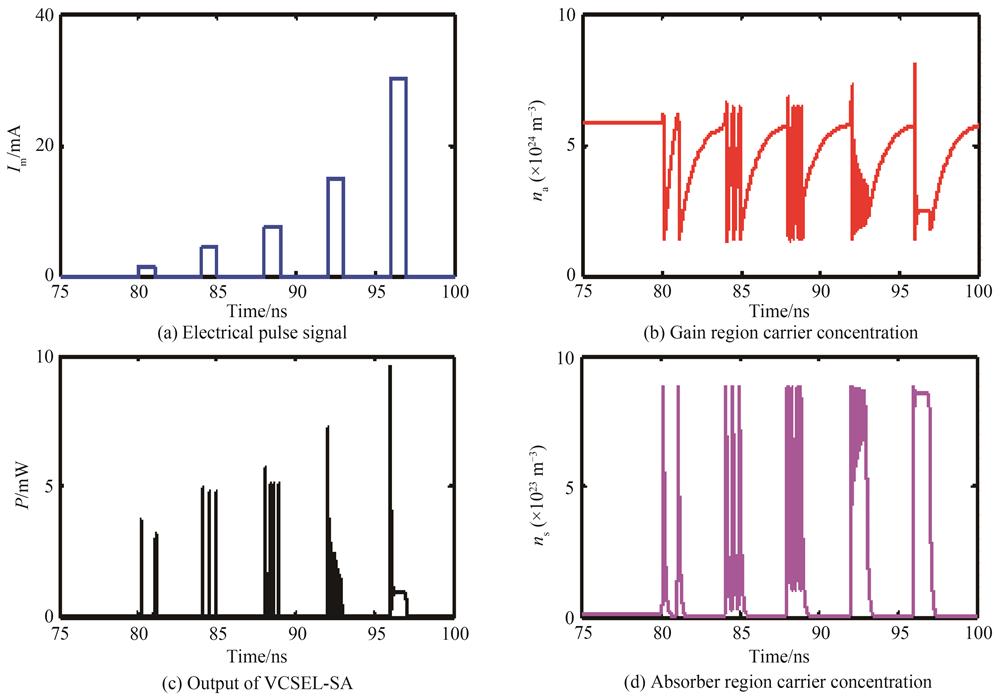

Fig. 2. The output of the VCSEL-SA for different modulation signal amplitude

Fig. 3. The output of the VCSEL-SA for modulation signals with different perturbation durations

Fig. 4. Output of VCSEL-SA under external disturbance

Fig. 5. Implementation of NOT logic operation

Fig. 6. Logic operation implementation of NAND gate and NOR gate

Fig. 7. Implementation of XOR logic operation

Fig. 8. Evolution of the VCSEL-SA's output with

Fig. 9. Influence of the input delay between two current modulation signals on the optoelectronic logic gate(NAND,NOR)

Fig. 10. The effect of noise on the implementation of optoelectronic logic gates(NAND,NOR,XOR)

|

Table 1. Typical VCSEL-SA parameters

Set citation alerts for the article

Please enter your email address