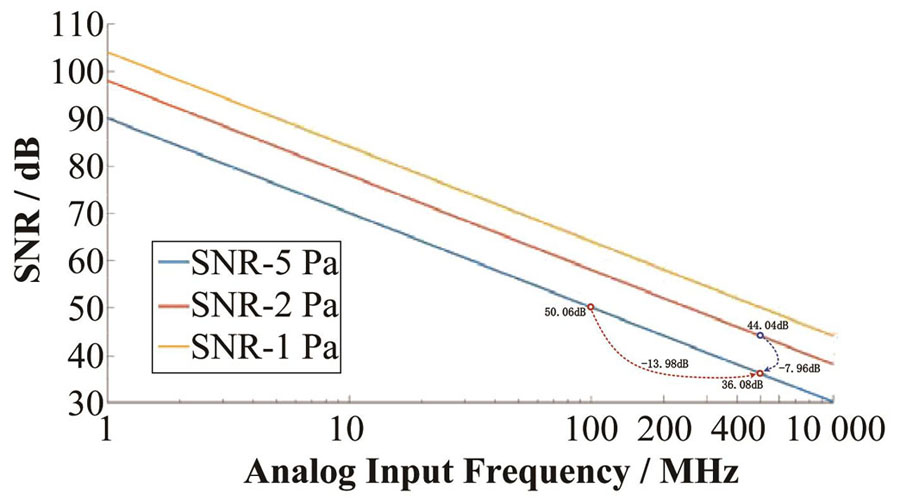

Digital measurement system based on ADCs (analog-to-digital converter) has higher requirement on the signal to noise ratio (SNR) of sampled data. Among all the factors, the jitter of sampling clock has the most prominent effect on SNR.

This study aims to design a clock circuit based on dual-loop phase-locked loop to reduce the jitter of digital measurement system input clock.

First of all, the influence of clock jitter on digital measurement system was analyzed. Then, the LMK04610 chip with dual loop PLL architecture of Texas Instruments was employed to design and implement a dual-loop phase-locked loop jitter cleaner circuit. The cores of this design were power supply design and the loop filter design. At last, the performance of the circuit was tested by using Rodschwarz phase noise analyzer.

After testing, the dual-loop phase-locked loop jitter cleaner circuit can reduce the jitter of the 62.475 MHz source clock from more than 7 ps to less than 2 ps with output frequency of 499.8 MHz. The SNR of the sampled data is close to the theoretical value.

Dual-loop phase-locked loop jitter cleaner circuit has a good result and can provide reference for designers of digital measurement system.