# **Temperature-switching logic in MoS<sub>2</sub> single transistors**\*

Xiaozhang Chen(陈孝章)<sup>1</sup>, Lehua Gu(顾乐华)<sup>2</sup>, Lan Liu(刘岚)<sup>1</sup>, Huawei Chen(陈华威)<sup>1</sup>, Jingyu Li(栗敬侯)<sup>1</sup>, Chunsen Liu(刘春森)<sup>3,†</sup>, and Peng Zhou(周鹏)<sup>1,‡</sup>

<sup>1</sup> The State Key Laboratory of ASIC and System, Department of Microelectronics, Fudan University, Shanghai 200433, China

<sup>2</sup> Department of Physics, State Key Laboratory of Surface Physics, Key Laboratory of Micro and Nano Photonic Structures (Ministry of Education),

and Institute for Nanoelectronic Devices and Quantum Computing, Fudan University, Shanghai 200433, China

<sup>3</sup> School of Computer Science, Fudan University, Shanghai 200433, China

(Received 17 June 2020; revised manuscript received 7 July 2020; accepted manuscript online 28 July 2020)

Due to their unique characteristics, two-dimensional (2D) materials have drawn great attention as promising candidates for the next generation of integrated circuits, which generate a calculation unit with a new working mechanism, called a logic transistor. To figure out the application prospects of logic transistors, exploring the temperature dependence of logic characteristics is important. In this work, we explore the temperature effect on the electrical characteristic of a logic transistor, finding that changes in temperature cause transformation in the calculation: logical output converts from 'AND' at 10 K to 'OR' at 250 K. The transformation phenomenon of temperature regulation in logical output is caused by energy band which decreases with increasing temperature. In the experiment, the indirect band gap of MoS<sub>2</sub> shows an obvious decrease from 1.581 eV to 1.535 eV as the temperature increases from 10 K to 250 K. The change of threshold voltage with temperature is consistent with the energy band, which confirms the theoretical analysis. Therefore, as a promising material for future integrated circuits, the demonstrated characteristic of 2D transistors suggests possible application for future functional devices.

Keywords: molybdenum disulfide (MoS<sub>2</sub>), logic, temperature dependence, mobility

PACS: 72.20.Pa, 81.05.Zx, 81.07.-b

## 1. Introduction

The successful exfoliation of monolayer graphene<sup>[1]</sup> initiated large-scale studies of two-dimensional (2D) materials, which have no dangling bonds, atomic thickness,<sup>[2]</sup> and van der Waals interactions.<sup>[3]</sup> To extend Moore's law, 2D materials with these characteristics have been applied to a variety of applications in integrated circuits, such as logic gates,<sup>[4]</sup> memories,<sup>[5]</sup> and central processing units.<sup>[6]</sup> However, these applications generally rely on traditional CMOS-based structures and follow the development methods of silicon-based circuits, which cannot take full advantage of the natural properties of 2D materials. Recently, a work innovatively constructed a 2D logic transistor with a new working principle,<sup>[7]</sup> implementing logic calculation in one single transistor, which saves 50% area in one unit. The logic gate of the traditional structure requires at least two transistors to realize the same logic calculation. This new working mechanism transistor not only shows a promising solution for future 2D electronic devices and circuit architectures, but also increases 2D integrated circuit density. For further application of this 2D logic transistor, further research is required on logical function modulated by multiple physical fields, especially the working temperature.

In this work, a full 2D logic transistor with a sandwich

**DOI:** 10.1088/1674-1056/aba9cf

structure (h-BN/MoS<sub>2</sub>/h-BN) is fabricated and its logic output at various environmental temperatures is measured. As the temperature changes, the logic output of the transistor switches between two output functions ('AND' and 'OR'), which means 2D logic transistors have application potential in extreme environments. This temperature switchable phenomenon is attributed to the modulation of temperature to energy band, specifically to mobility and threshold voltage. To confirm this explanation, detailed experimental data and theoretical calculations are provided.

### 2. Experiment

To study the temperature dependent characteristic of a  $MoS_2$  logic transistor, a device was fabricated on an  $Al_2O_3$  substrate, and measured by cryogenic probe station with a temperature range of 7 K to 250 K. Firstly, multilayer  $MoS_2$  and h-BN were exfoliated with tapes on a sacrificial layer. Then, wet transfer method was used to stack the sandwich structure layer by layer. Next, electron beam lithography was applied to define the location of electrodes, especially the full alignment of the bottom and top gates, in case of non-overlapping region appearance. Finally, a 5 nm Cr (adhesion layer) and a 30 nm Au (metal) layer were deposited as electrodes by electron beam

\*Project supported by the National Natural Science Foundation of China (Grant Nos. 61925402, 61851402, and 61734003), Science and Technology Commission of Shanghai Municipality, China (Grant No. 19JC1416600), National Key Research and Development Program of China (Grant No. 2017YFB0405600), and Shanghai Education Development Foundation and Shanghai Municipal Education Commission Shuguang Program, China (Grant No. 18SG01).

<sup>†</sup>Corresponding author. E-mail: chunsen\_liu@fudan.edu.cn

<sup>‡</sup>Corresponding author. E-mail: pengzhou@fudan.edu.cn

© 2020 Chinese Physical Society and IOP Publishing Ltd

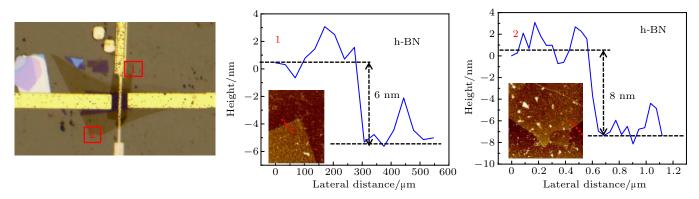

evaporator. The temperature dependence of the electrical characteristic was measured in a vacuum, while fabrication processes were realized in the normal atmosphere. The thickness of h-BN was confirmed by atomic force microscope (Fig. A1): top dielectric was 6 nm; bottom dielectric was 8 nm; thickness of channel material  $MoS_2$  was around 5–6 nm; channel width and length were 3 µm and 8.5 µm, respectively.

#### 3. Results and discussion

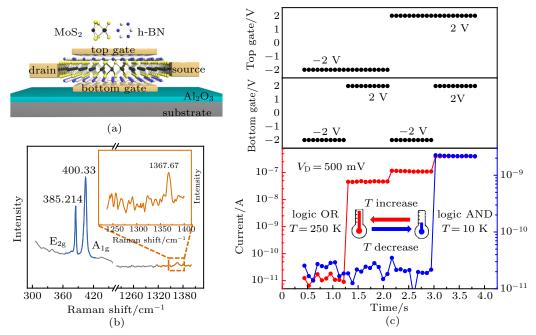

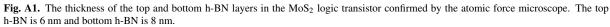

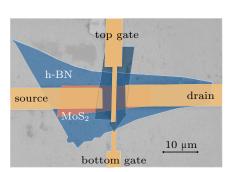

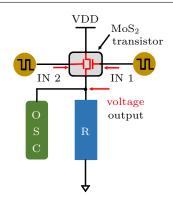

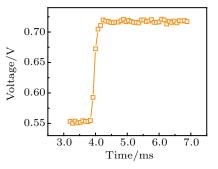

Figure 1(a) presents a three-dimensional schematic structure of the  $MoS_2$  logic transistor:  $MoS_2$  is the channel layer, connecting with the drain and source electrodes; h-BN is the dielectric layer, blocking the connection between the gate and channel; the gates serve as the terminals of signal input, IN 1 for the top gate and IN 2 for the bottom gate. When inputs of IN 1 and IN 2 are low voltages, the input signal of the device is defined as IN-00. When either input of IN 1 and IN 2 is a high voltage, the input signal of the device is defined as IN-10 or IN-01. When inputs of IN 1 and IN 2 are high voltages, the input signal of the device is defined as IN-11. The high output current of the MoS<sub>2</sub> logic transistor is defined as '1' state, while low output current is '0' state. The false-colored scanning electron microscope (SEM) image of the real device is shown in Fig. A2, which shows an accurate alignment of the two gates. A previous study<sup>[8]</sup> showed that MoS<sub>2</sub> exhibits high electron mobility<sup>[9]</sup> and a large band gap,<sup>[10]</sup> which indicates that MoS<sub>2</sub> has the potential to meet the requirements of logical application. The components of channel and dielectric are confirmed by Raman spectroscopy (Fig. 1(b)), which shows two characteristic peaks  $(A_{1g}, E_{2g})$  of  $MoS_2^{[11]}$  and one characteristic peak of h-BN.<sup>[12]</sup> When a series of identical input signals are applied to a logic transistor (IN-00, IN-01, IN-10, IN-11, voltage amplitude of 2 V), the channel current exhibits outputs of logic 'AND' at low temperature (10 K) and 'OR' at high temperature (250 K), revealing the temperatureswitching characteristic of the MoS<sub>2</sub> logic transistor, as shown in Fig. 1(c). Due to the structure and working principle of the transistor, the directly measured output signal of the MoS<sub>2</sub> logic transistor is current. The circuit of the voltage-in currentout test system is plotted in Fig. A3. To transfer the current signal into a voltage signal, an additional resistor is introduced into the testing system and transforms the channel current into its partial voltage, as shown in Fig. A4. Figure A5 is the partial voltage of the resistor ( $R = 220 \text{ k}\Omega$ ), showing a recognizable voltage-in voltage-out 'OR' logic gate function. Since the current output can be simply transferred into voltage, we take the current signal as evaluation criteria in the following part of this article.

Fig. 1. Device structure and characterization of  $MoS_2$  logic transistor. (a) Three-dimensional sectional view of  $MoS_2$  logic transistor.  $MoS_2$  serves as channel material; h-BN serves as dielectric material; top and bottom gates are used to input logic signal (voltage); drain and source are used to collect output signal (current). (b) Raman spectra of  $MoS_2$  logic transistor, obtained by laser with 532 nm wavelength and 50  $\mu$ W energy. The overlapped region shows characteristic peaks of the two materials ( $MoS_2$  and h-BN). (c) Temperature switchable logic output of  $MoS_2$  logic transistor. Continuous  $\pm 2$  V is provided as input signal through top and bottom gates; channel current is collected as an output signal through drain and source; the drain voltage is 500 mV. The output characteristic of this device can be transformed into voltage by load resistance which is shown in Figs. A3–A5.

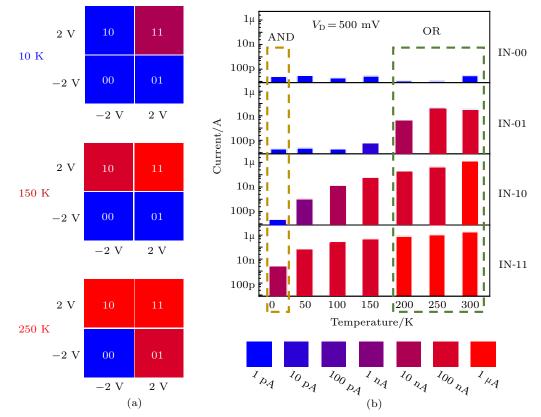

When the input voltages of the bottom gate ( $V_{BG}$ ) and top gate ( $V_{TG}$ ) are plotted as *x*- and *y*-axis, respectively, the output of current distribution density mapping can be divided into four regions, IN-00, IN-01, IN-10, and IN-11, obtained by drain voltage ( $V_D$ ) of 500 mV. The mean value of the output channel current is selected as the output state and is used as the parameter to transform output state into a color squire, and four color-squires are composed together as one part to illus-

trate the logic function of the MoS<sub>2</sub> logic transistor at different temperatures. The basic color squires are blue (R = 0, G = 0)B = 255) and red (R = 255, G = 0, B = 0), representing the current values 1 pA and 1 µA. At 10 K, only the IN-11 region is in red, corresponding with logic 'AND', which means the channel can only be opened when both gates input high voltages. With the increase of temperature (at 150 K), the color of region IN-10 begins to turn red, which means the device is in a transition state of logical function. When the temperature rises to 250 K, the color of three regions (IN-01, IN-10, IN-11) turns to red, corresponding with logic 'OR', which means the channel can be opened by either gate (Fig. 2(a)). Extracting the average value of current in four stages at different temperatures, we plot Fig. 2(b). When the temperature increases, the output current of regions IN-00 and IN-11 is stable, whereas the output current of regions IN-10 and IN-01 changes, which leads to the transformation of logic output. This shows a dynamic change process of temperature-switching phenomenon.

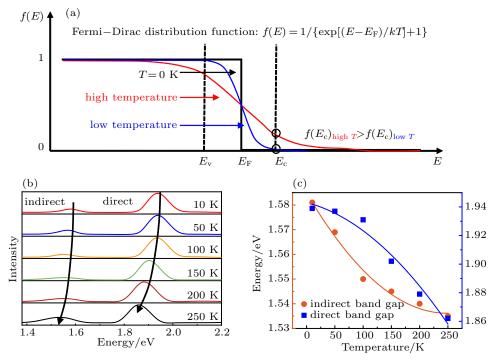

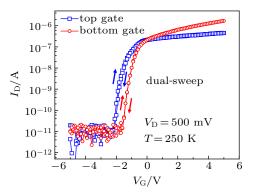

Figure 2 indicates that the key element of logical transformation is the output transformation of regions IN-01 and IN-10. The transformation mechanism can be demonstrated by the Fermi–Dirac distribution function. Figure 3(a) shows that the occupy probability of electrons, symbolized as f(E), increases with the increase of temperature. In f(E) = $1/\{\exp[(E - E_{\rm F})/kT] + 1\}$ , f(E) is affected by two factors: one is  $E - E_{\rm F}$ , standing for the band gap variation, the other is kT, standing for the extra carrier energy provided by temperature. With the increase of temperature, the increase of kT leads the increase of f(E), which means the probability of electron occupation in  $E_c$  is higher. Besides kT directly affected by temperature,  $E - E_F$  is also impacted by temperature. Previous studies showed that the band gap of MoS<sub>2</sub> decreases with the increase of temperature.<sup>[13,14]</sup> Figure 3(b) is the photoluminescence spectrum of the MoS<sub>2</sub> logic transistor at different temperatures, which shows a significant indirect band gap shift from 1.581 eV at 10 K to 1.535 eV at 250 K and direct band gap shift from 1.939 eV at 10 K to 1.862 eV at 250 K (Fig. 3(c)). Based on the band gap variation phenomenon,  $E - E_F$  shows a decreasing tendency with the increase of temperature, which also leads to an increase of f(E). So the two aspects have the same increase tendency for f(E), which means higher temperature generates a higher probability of electron occupation in the bottom of conduction band  $E_{\rm c}$ , corresponding to Fig. 3(a). Therefore, the temperature switchable phenomenon is caused by the band gap variation and carrier energy directly provided by temperature. Furthermore, figure A6 presents the dual-sweep transfer curves of the top and bottom interfaces, which shows negligible hysteresis of electrical characteristics caused by charge trapping. So, the influence of charge trapping/releasing effect on channel current can be ignored.

**Fig. 2.** Temperature dependence of MoS<sub>2</sub> logic transistor. (a) The current density distribution diagram at different temperatures. (b) The current distribution histogram of four states at different temperatures. The asymmetric performance of IN-01 and IN-10 is caused by different thickness of h-BN, which leads to the abnormal logic function (neither 'OR' nor 'AND') at 50 K, 100 K, and 150 K. Both (a) and (b) have the same input voltage ( $V_{TG}$ ,  $V_{BG} = \pm 2$  V),  $V_D = 500$  mV, and color bar.

Fig. 3. The temperature dependence of Fermi–Dirac distribution function of  $MoS_2$  logic transistor. (a) Schematic diagrams of temperature influence on the Fermi–Dirac distribution function. The schematic diagram shows the change process of Fermi–Dirac distribution function with temperature intuitively. (b) Photoluminescence spectrum of  $MoS_2$  logic transistor at different temperatures (10–250 K). The excitation wavelength is 532 nm; power is 40  $\mu$ W; integration time is 10 s. (c) The decrease tendency of direct and indirect band gaps of  $MoS_2$  logic transistor with increasing temperature.

After analyzing the transition principle of logical output in a dual gate  $MoS_2$  transistor, figure 4 further illustrates the temperature-dependent current characteristics with detailed experimental data. The channel current is calculated by theoretical equations under different drain voltage conditions. The following equations (1) and (2) apply to the linear region and saturated region, respectively:

$$I_{\rm D} = \frac{1}{2} \mu C_{\rm ox} \frac{W}{L} \left[ 2 \left( V_{\rm G} - V_{\rm T} \right) V_{\rm D} - V_{\rm D}^2 \right], \ 0 < V_{\rm D} < V_{\rm G} - V_{\rm T}, (1)$$

$$I_{\rm D} = \frac{1}{2} \mu C_{\rm ox} \frac{W}{L} \left( V_{\rm G} - V_{\rm T} \right)^2, \quad V_{\rm D} > V_{\rm G} - V_{\rm T}, \tag{2}$$

where  $\mu$  is the carrier mobility,  $C_{\text{ox}}$  is the gate capacitance, W is the channel width, L is the channel length,  $V_{\text{G}}$  is the gate– source voltage, and  $V_{\text{T}}$  is the threshold voltage of the transistor. In these equations, both  $V_{\text{T}}$  and  $\mu$  are relevant to temperature, resulting in the temperature dependence of the channel current and logical output.

The transistor mobility is extracted from

$$g_{\rm m} = \mu C_{\rm ox} \frac{W}{L} V_{\rm D}, \qquad (3)$$

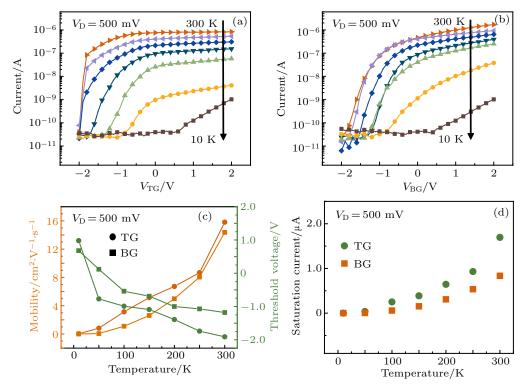

where  $g_{\rm m}$  is the transconductance, defined as  $g_{\rm m} = dI_{\rm D}/dV_{\rm G}$ and extracted from Figs. 4(a) and 4(b); the gate capacitance  $C_{\rm ox} = \varepsilon_{\rm ox}/d_{\rm ox}$ ,  $\varepsilon_{\rm ox} = 3.5416 \times 10^{-11}$  F/m is the dielectric constant of h-BN, and  $d_{\rm ox}$  is the thickness of h-BN. Note that the maximum values of  $g_{\rm m}$  were used to extract the channel mobility values.<sup>[15]</sup> Figure 4(c) shows the dependence of the threshold voltage on temperature, extracted from Figs. 4(a) and 4(b). The threshold voltage is obtained by the intercept generated by the tangent line of  $I_DV_G$  and the x-axis. As the temperature increases, two surface channels controlled by the bottom gate and top gate show a visible negative shift, which means the increase of temperature reduces the energy required for electron transition. At the same time, the decrease of  $V_{\rm T}$  shows a reduction of band gap, which is consistent with Fig. 3(b). Figure 4(c) also shows the temperature dependence of surface channel mobility extracted from transfer characteristic curves at various temperatures (Figs. 4(a) and 4(b)). As can be seen from the picture, the channel mobility of both the bottom gate and top gate is increased with temperature and the highest value is  $15.8 \text{ cm}^2 \cdot \text{V}^{-1} \cdot \text{s}^{-1}$  at 300 K, which means the mobility is limited by scattering from charge impurities.<sup>[16]</sup> According to the physics of semiconductor devices, the higher the temperature is, the faster the carrier moves. Therefore, the carrier is less affected by the same attraction and repulsion, which means the effect of charge-impurities scattering is weaker at higher temperatures.<sup>[17]</sup> For  $\mu$  and  $-V_{\rm T}$  showing an increased relationship with temperature, the channel saturation current is positively correlated with temperature, which is consistent with Fig. 4(d) (the channel current extracted from Figs. 4(a) and 4(b) at 2 V).

With 2D materials, the logic function ('OR' and 'AND' gates) can be achieved in a single transistor. Compared with traditional transistor technology which needs at least two transistors to build a logic gate, this logic transistor architecture shows obvious area-efficiency strength. Furthermore, the tem-

perature switchable phenomenon opens up the potential for tailor-made 2D circuits, such as reconfigurable circuits. In reconfigurable circuits, one circuit design can achieve more than one function in different temperature configurations. Therefore, temperature-switchable behavior will be helpful in tailormade reconfigurable circuits based on 2D materials in the future. In this work, a colorful logic map (Fig. 2(a)) is proposed, which is helpful in the construction of a reconfigurable circuit.

Fig. 4. Temperature dependence of mobility, threshold voltage, and saturation current. (a) and (b) The transfer characteristics of the top gate and bottom gate in  $MoS_2$  logic transistor. Panels (a) and (b) use the same graphic symbol. (c) The extracted mobility and subthreshold voltage at various temperatures. (d) The saturation current extracted from (a) and (b) at 2 V under various temperatures.

#### 4. Conclusion and perspectives

In this work, we study the temperature dependence of an  $MoS_2$  logic transistor, finding that the logical output result changes from 'AND' to 'OR' with the increase of temperature. The transformation of output between 'AND' and 'OR' at different temperatures is caused by the energy band gap de-

creasing and extra energy provided by temperature. With the increase of temperature, both direct and indirect band gaps of  $MoS_2$  show a remarkable decrease, which is confirmed both by the photoluminescence spectrum and threshold voltage shift. The temperature switchable phenomenon of  $MoS_2$  logic transistors has application prospects for extreme environments.

## Appendix A

Fig. A2. The false-colored SEM image of  $MoS_2$  logic transistor. The blue represents h-BN; red represents the  $MoS_2$ ; yellow represents electrodes.

Fig. A3. The circuit of  $MoS_2$  logic transistor that outputs the current signal. IN 1 and IN 2 separately represent the input signal from the top gate and bottom gate. The input voltage is generated by Keithley 4200 A semiconductor parameter analyzer. And output current is measured by the same instrument.

Fig. A4. The circuit of  $MoS_2$  logic transistor that outputs voltage signal. To transfer output current into voltage, a resistor (220 k $\Omega$ ) is induced into the circuit. An oscilloscope is used to measure the partial voltage of the resistor.

Fig. A5. Diagram of the voltage output of  $MoS_2$  logic transistor. The resistance is 220 k $\Omega$  and the measuring instrument is oscilloscope (internal resistance = 1 M $\Omega$ ). However, the oscilloscope internal resistance is not large enough for two-dimensional material devices, which makes the branch current of the oscilloscope very big. Therefore the voltage output of the device has a low on–off ratio after transformation.

Fig. A6. The dual-sweep transfer curves of MoS<sub>2</sub> logic transistor. The zero hysteresis indicates that the interface charge trapping is negligible;  $V_D = 500 \text{ mV}$ , T = 250 K.

#### References

- Novoselov K S, Geim A K, Morozov S V, Jiang D, Zhang Y, Dubonos S V, Grigorieva I V and Firsov A A 2004 *Science* 306 666

- [2] Desai S B, Madhvapathy S R, Sachid A B, Llinas J P, Wang Q, Ahn G H, Pitner G, Kim M J, Bokor J and Hu C 2016 Science 354 99

- [3] Novoselov K, Mishchenko A, Carvalho A and Neto A C 2016 Science 353 aac9439

- [4] Huang M, Li S, Zhang Z, Xiong X, Li X and Wu Y 2017 Nat. Nanotechnol. 12 1148

- [5] Zhang Z, Wang Z, Shi T, Bi C, Rao F, Cai Y, Liu Q, Wu H and Zhou P 2020 InfoMat 261 290

- [6] Wachter S, Polyushkin D K, Bethge O and Mueller T 2017 Nat. Commun. 8 14948

- [7] Liu C, Chen H, Hou X, Zhang H, Han J, Jiang Y G, Zeng X, Zhang D W and Zhou P 2019 Nat. Nanotechnol 14 662

- [8] Yang Z, Wu Z, Lyu Y and Hao J 2019 InfoMat 1 98

- [9] Yu Z, Ong Z Y, Li S, Xu J B, Zhang G, Zhang Y W, Shi Y and Wang X 2017 Adv. Funct. Mater. 27 1604093

- [10] Radisavljevic B, Radenovic A, Brivio J, Giacometti i V and Kis A 2011 Nat. Nanotechnol. 6 147

- [11] Li H, Zhang Q, Yap C C R, Tay B K, Edwin T H T, Olivier A and Baillargeat D 2012 Adv. Funct. Mater. 22 1385

- [12] Jin C, Kim J, Suh J, Shi Z, Chen B, Fan X, Kam M, Watanabe K, Taniguchi T and Tongay S 2017 Nat. Phys. 13 127

- [13] Plechinger G, Schrettenbrunner F X, Eroms J, Weiss D, Schueller C and Korn T 2012 Phys. Status. Solidi. Rapid. Res. Lett. 6 126

- [14] Hannewald K, Stojanović V, Schellekens J, Bobbert P, Kresse G and Hafner J 2004 Phys. Rev. B 69 075211

- [15] Das S, Chen H Y, Penumatcha A V and Appenzeller J 2012 Nano Lett. 13 100

- [16] Neamen D A 2012 Semiconductor physics and devices: basic principles (New York: McGraw-Hill)

- [17] Radisavljevic B and Kis A 2013 Nat. Mater. 12 815