# HEPS 快速轨道反馈系统网络拓扑结构的设计与实现

高国栋<sup>1,2</sup> 刘 鹏<sup>1</sup> 龙锋利<sup>1,2</sup> 季大恒<sup>1</sup> 叶 强<sup>1</sup> 杜垚垚<sup>1</sup> 刘 智<sup>1</sup> 随艳峰<sup>1,2</sup> 岳军会<sup>1</sup> 唐旭辉<sup>1,2</sup> 魏书军<sup>1,2</sup> 曹建社<sup>1,2</sup> 1(中国科学院高能物理研究所 北京 100049)

摘要 快速轨道反馈(Fast Orbital Feedback, FOFB)系统是影响高能同步辐射光源(High Energy Photon Source, HEPS)轨道稳定性的重要因素之一,在设计时应尽可能提高FOFB系统的有效反馈带宽。基于该需求,为HEPS 的FOFB系统设计了两层环路集中计算式的系统网络拓扑结构,并在此基础上设计完成了FOFB系统信号传输链路的可编程阵列逻辑(Field Programmable Gate Array, FPGA)固件算法逻辑,内容包括束流位置获取、环路数据传输、FOFB算法、电源控制接口以及系统测试等多个部分。经实验室测试验证,当前结构下的FOFB系统总延迟时间约为140μs,满足HEPS装置对FOFB系统有效反馈带宽的需求。

关键词 高能同步辐射光源,快速轨道反馈,FPGA,高速数据传输,数字信号处理

中图分类号 TL506

**DOI:** 10.11889/j.0253-3219.2023.hjs.46.050102

# Design and implementation of network topology for HEPS fast orbit feedback system

GAO Guodong<sup>1,2</sup> LIU Peng<sup>1</sup> LONG Fengli<sup>1,2</sup> JI Daheng<sup>1</sup> YE Qiang<sup>1</sup> DU Yaoyao<sup>1</sup> LIU Zhi<sup>1</sup> SUI Yanfeng<sup>1,2</sup> YUE Junhui<sup>1</sup> TANG Xuhui<sup>1,2</sup> WEI Shujun<sup>1,2</sup> CAO Jianshe<sup>1,2</sup>

1(Institute of High Energy Physics, Chinese Academy of Sciences, Beijing 100049, China)

2(University of Chinese Academy of Sciences, Beijing 100049, China)

Abstract [Background] HEPS (High Energy Photon Source) needs to control the beam orbit change within 10% of the cluster size within a certain frequency. In order to meet the beam orbit stability requirements in HEPS, it is necessary to establish a fast orbit feedback (FOFB) system. [Purpose] This study aims to design and implement an effective feedback bandwidth of FOFB system that is greater than 500 Hz, and the delay of the whole system is less than 160 μs. [Methods] Based on this requirement, a two-layer communication of loop centralized computing system network topology was designed and implemented for FOFB system of HEPS. And on this basis, the FPGA (field-programmable gate array) firmware algorithm of the signaling pathway of FOFB system was realized, including beam position acquisition, loop data transmission, FOFB algorithm, power control interface and the testing logic. [Results] The measurement and analysis results show that each module in the data transmission link of the FOFB system can be used normally, and the total delay time of the system is about 140.46 μs, which has reached the intended design target. [Conclusions] The FOFB design of this study lays a foundation for the future construction,

Corresponding author: CAO Jianshe, E-mail: caojs@ihep.ac.cn

Received date: 2022-10-12, revised date: 2023-01-07

中国科学院青年创新促进会基金(No.Y202005)资助

第一作者: 高国栋, 男, 1997年出生, 2019年毕业于四川大学, 现为博士研究生, 研究领域为加速器束流测量与控制系统研究

通信作者: 曹建社, E-mail: caojs@ihep.ac.cn 收稿日期: 2022-10-12, 修回日期: 2023-01-07

Supported by Youth Innovation Promotion Association of Chinese Academy of Sciences Fund (No.Y202005)

First author: GAO Guodong, male, born in 1997, graduated from Sichuan University in 2019, doctoral student, focusing on beam measurement and control system of accelerator

optimization and debugging of FOFB system on HEPS storage ring with good flexibility and scalability, providing a feasible solution for the future establishment of fast orbit feedback system in other storage rings.

Key words HEPS, Fast orbit feedback, FPGA, High speed data transmission, Digital signal processing

作为第四代同步辐射光源,高能同步辐射光源(High Energy Photon Source, HEPS)需要将一定频率内的束流轨道变化控制在10%束团尺寸以内[1]。为了满足 HEPS 中束流轨道稳定性的要求,建立快速轨道反馈(Fast Orbit Feedback, FOFB)系统是必要的。FOFB 系统根据储存环上束流位置探测器(Beam position Monitor, BPM)测得的位置信息,计算得到储存环中各个快校正子需要设置的工作电流,从而实现校正子电源的快速响应。HEPS 要求FOFB 系统的有效反馈带宽应不低于500 Hz,这项指标将直接影响HEPS的最终性能[2]。

在FOFB系统中,FOFB算法在快速轨道反馈控 制器(Feedback Orbit Controller, FOC)中实现,每个 FOC 都需要在每次计算时收集到全环的 BPM 位置 信息,利用响应矩阵计算每个快校正子所需的电流 后,将结果发送给对应的快校正子电源。FOFB系 统的网络拓扑结构用于描述系统中BPM、快校正子 电源与FOC之间如何布局和连接,它直接影响了 FOFB系统的数据传输延时和FOFB算法的结构,是 整个FOFB系统的基础。国内外主流的FOFB系统 拓扑结构有两种:一种是链式结构,如上海光源 (Shanghai Synchrotron Radiation Facility, SSRF)[3]和 台湾光子源(Taiwan Photon Source, TPS)[4]等;另一 种是环路结构,如美国国家同步辐射光源(National Synchrotron Light Source-II, NSLS II)、美国先进光 子源升级(Advanced Photon Source-Upgrade, APS-U)和巴西光源(Sirius)等[5-8]。其中,APS-U与Sirius 作为与HEPS一样的第四代光源,均采用两层环路 的集中计算式结构,并使用现场可编程门阵列 (Field Programmable Gate Array, FPGA)作为FOC 的计算核心,通过FPGA的高速数据传输接口实现 系统各模块之间的通信,最终在主控制器中完成快 校正子电流的计算。本文将在已完成的中国科学院 高能物理研究所自研数字BPM电子学和HEPS快校 正子数字电源的基础上,为HEPS的FOFB系统设计 了一种专用的且更为优化的双层环路式网络拓扑结 构,同时介绍了基于该结构的数据传输链路和各模 块之间的数据传输方法,估算FOFB系统各部分的 延时,并通过仿真和测试验证了该结构的可行性。 本文介绍的FOFB系统结构和数据传输方法在满足 系统有效反馈带宽的同时,兼具灵活性和可拓展性, 可以在未来应用于HEPS工程中。

# 1 FOFB系统结构

## 1.1 基本结构

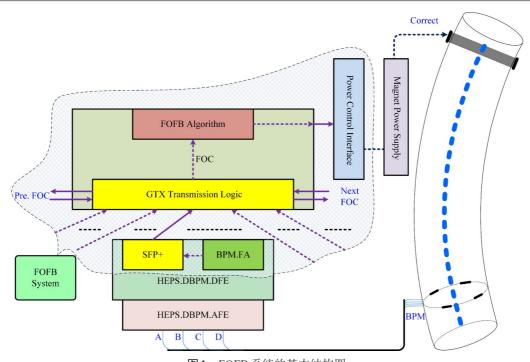

作为一个反馈控制系统,可以将FOFB系统分为三个子系统,分别是BPM系统、FOFB控制器系统和快校正子系统(包含快校正电源、磁铁与真空盒),三个系统均使用FPGA作为核心芯片。其中,BPM系统作为整个控制的传感器,用于实时接收和传递束流位置信息;FOFB控制器系统是整个系统的控制中枢,需要处理信息并计算得到校正子电源的给定值;而快校正子系统则是系统的执行器,负责接收控制器送来的给定值并将其作用于束流。为了提高控制精度,BPM每发出一组数据就需要完成一次闭环控制,控制频率为BPM的FA数据输出频率,即22 kHz。

在每次闭环控制中,首先由BPM探头接收束流信号并通过电缆传递给BPM电子学,并在BPM模拟前端板卡(Analog Front-end Electronics, AFE)中实现BPM信号的窄带滤波、增益控制和ADC采样等功能。其次在BPM数字前端板卡(Digital Front-end Electronics, DFE)中依次完成数字信号处理、束流位置计算、数据编码发送等任务<sup>[9]</sup>。然后,通过SFP+(Small Form-factor Pluggables)接口由FOC接收BPM发送的束流位置数据,完成FOFB算法得到快校正子电流,并将结果经编码后通过电源控制接口发送给后端的快校正子电源控制器(Power Supply Controller, PSC)。快校正子电源将接收到的数据转化为负载电源电流给定值作用于快校正子,最后,通过快校正子控制储存环束流的横向位置,FOFB系统的基本结构如图1所示<sup>[10]</sup>。

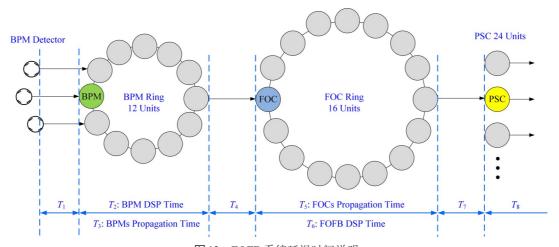

# 1.2 网络拓扑结构

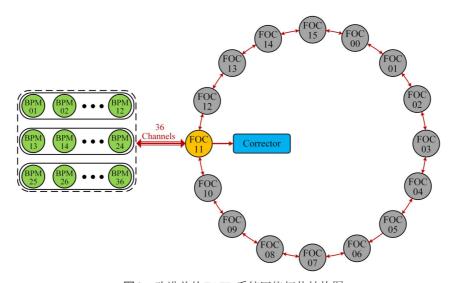

在设计周长为1360 m的 HEPS 储存环上,共设有576个BPM和384个快校正子,每个快校正子需要一台快校正子电源控制。储存环上共设有16个控制站,每个控制站都需要有一台FOC,它的任务是接收全环共576个BPM的所有FA数据,完成计算后将结果(即校正子设定点)发送给后端的PSC中。为了确保反馈环路有足够的带宽,在短时间内分发来自所有存储环BPM的22 kHz数据,设计了两层通信架构,以确保满足FOFB系统的时间预算。第一层是本地BPM和每个站点FOC之间的通信,第二层是

图1 FOFB系统的基本结构图 Fig.1 Basic structure diagram of FOFB system

整个存储环中不同站点FOC之间的通信。

为了将数据传输的延时降至最低,首先设计了一种网络拓扑结构,如图2所示。在储存环中共设置48个束测站点,每个站点中放置12台BPM,每个FOC同时点对点连接三个本地站共48台BPM,而全环的16台FOC首尾依次相连构成FOC数据环路,保证任意一台FOC都可以接收到所有的BPM数据。同时基于硬件、延时等因素考虑,HEPS将采用快校正子电流的分布式计算方法,即在FOC中只计算对

应的24个快校正子的设定电流,再将计算结果转化为电流后直接发送给与FOC相连的24个PSC中。基于此结构可以最大程度减少BPM与FOC之间通信的延时,但是由于一个FOC需要同时与36台BPM点对点连接,FOC需要同时使能至少36个高速数据传输接口,一路接口的功耗约为2W,因此,该方案对于FOC的硬件和软件都提出了很高的要求,同时由于高功耗使系统的可靠性无法得到保证。

图2 改进前的FOFB系统网络拓扑结构图 Fig.2 Original network topology of FOFB system

鉴于上述原因,我们对系统的网络拓扑结构做 出了改进,改进后的系统结构如图3所示。在之前 方案的基础上将每个束测站中的12台BPM首尾相连构成BPM数据环路,并选取其中一台BPM与后

端的FOC相连。FOC同时接收三个束测站的BPM数据,因此,改进结构后FOC只需要使能5个高速数据传输接口,极大程度上减少了功耗。其中BPM与BPM之间用2m高速铜缆连接,BPM与FOC、FOC与FOC之间用50m多模万兆光纤连接,数据传输速

率均为10 Gb·s¹。相比于最初的方案,改进后的FOFB系统网络拓扑结构仅在BPM与FOC的通信间增加了少量延迟的前提下,降低了FOC硬件的功耗及设计难度,同时也有利于未来在HEPS中的FOFB系统搭建、优化和调试。

图 3 改进后的FOFB 系统网络拓扑结构图 Fig. 3 Improved network topology of FOFB system

# 2 基于双层环形网络的数据传输链路设计

使用 FPGA 的可编程逻辑(Programmable Logic,PL)资源,基于FOFB系统的双层拓扑结构网络,为系统中的BPM、FOC和PSC分别设计相应的FPGA固件程序,从而在系统中搭建从BPM到FOC的数据传输链路,最终实现BPM的ADC数据到快校正子电源之间数据的处理与传输功能。

### 2.1 数据传输单元

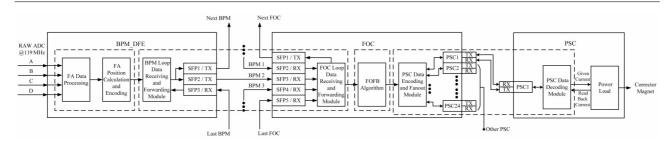

在 HEPS 中 FOFB 系统由 576 套 BPM、16 套 FOC 和 384 台快校正子电源搭建而成,在设计固件程序时应保证环中所有的 BPM、FOC 与 PSC 都有着相同的固件程序,以便于储存环中任意的一台BPM、FOC或 PSC 可以放置在网络结构中与之对应的任意节点上,从而很大程度地减少了工程的工作量。基于该原则,可以用一个数据传输单元来表述

FOFB系统双层环形网络的数据传输链路的具体实现过程,数据传输单元由一块BPM数字信号处理板卡、一套FOC和一台PSC构成,具体结构如图4所示。

如图4所示,依照在数据传输链路中的功能将数据传输单元中的各个模块分为4个部分:第一部分包含了FA数据处理模块和FA位置计算与编码模块,在BPM中实现了束流位置数据的输出功能;第二部分由BPM、FOC环路数据接收转发模块组成,用于搭建BPM与FOC之间的数据传输链路,实现了束流位置环路传输功能;第三部分是FOFB算法模块,完成了从束流位置信息到校正子强度的计算;第四部分由PSC数据的编码、解码模块组成,是FOFB系统的电源控制接口,用于实现FOC与PSC之间的数据传输功能。

图 4 数据传输单元结构图 Fig.4 Structure diagram of data transmission unit

### 2.2 FA数据的输出

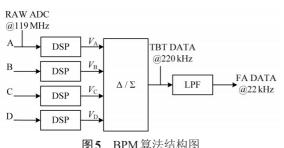

BPM电子学可以提供三种束流位置数据,分别是逐圈(Turn By Turn,TBT)位置数据、快获取(Fast Acquisition, FA)位置数据,其中 FA 数据将用于FOFB系统,数据输出频率为22 kHz,位置分辨率应小于0.3 μm。 FA 数据通过BPM 数字信号处理板卡上的 ZYNQ 芯片对 ADC 采样数据进行数字信号处理板卡上的 ZYNQ 芯片对 ADC 采样数据进行数字信号处理后得到,算法结构如图 5 所示。 ADC 首先以119 MHz的采样频率对经射频信号调理后的束流信号进行带通采样,之后对信号进行零中频变换和多级滤波抽取,用差和比公式计算出束流的TBT位置数据,最后再经过10倍低通滤波抽取后得到FA束流位置数据[1-3]。

Fig.5 Schematic diagram of BPM algorithm

在得到FA数据之后,还需要对其进行编码,编码后的数据帧中包含束流X方向位置、束流Y方向位置、BPM地址信息、FA时间信息和校验位,其中,BPM地址信息用于记录当前BPM在FOFB系统中的物理位置,FA时间信息用于记录FA数据的输出时间,校验位采用奇偶校验方式,在数据传输的每一个站点都对数据帧做误码检测。经编码后的数据帧将直接发送给后端的BPM环路数据接收转发模块以便于完成环路数据传输,数据帧的输出频率为22kHz,与FA数据同步。

### 2.3 束流位置传输

FOFB 系统将使用 FPGA 高速收发器(Gigabyte Transceiver X,GTX)完成环路中束流位置数据帧的

传输,GTX是集成于FPGA内部的高速串行接口,底层采用8b/10b编码,数据频率为125MHz,数据传输速率最高可达到10.3125Gb·s<sup>-1[14-15]</sup>。基于FOFB系统的双层环形网络,分别为BPM和FOC配置GTX接口的驱动程序,在BPM中最少应使能3个数据通道,FOC中最少应使能5个数据通道,设定数据传输速率为10Gb·s<sup>-1</sup>。

数据接收转发模块是实现储存环中束流位置环路传输的核心模块,其性能将直接决定了束流位置传输的总延时。在模块中将接收的多路GTX数据组合为一路数据后转发给下一级,是一个多通道输入单通道输出的模块,且在模块中数据流的接收和发送是同时进行的。

以FOC环路数据接收转发模块为例,需要同时接收3个BPM通道和一个FOC通道的数据共4个通道的数据,并分别使用4个FIFO存储器暂存收到的数据。在转发逻辑中,需要给每一个接收通道设定一个优先级,基于传输延时考虑,BPM通道的优先级应高于FOC通道。若某一时刻有多个FIFO中有数据,则根据设定的优先级规则发送优先级更高通道FIFO中的数据,从而在避免多余延时的前提下实现多路数据转化为一路数据的输出。与此同时,设定相应逻辑使得每个数据帧都在BPM环路或FOC环路中走完整的一圈,在实现环路数据实时更新的同时尽可能减小数据带宽。

当前束流位置传输方案可以在不改变BPM与FOC固件程序的前提下,在FOFB系统网络拓扑结构中任意增加或减少BPM或FOC的个数,从而使得整个系统兼具灵活性和可拓展性,有利于未来HEPS中FOFB系统的搭建、优化和调试。

# 2.4 FOFB算法

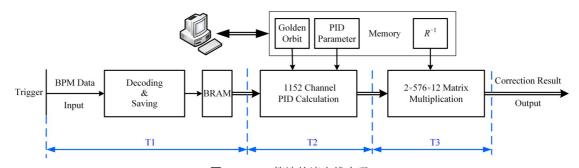

FOFB 算法模块运行于 FOC 中,是一个功能完整且有较好移植性能的计算核心。为了平衡 FPGA 内部资源损耗和数据处理延时,充分利用 FPGA 的高速并行计算特点,将以流水线形式处理数据,通过

与BPM 数据输出同步的、频率为22 kHz的外部脉冲信号触发,周期性计算每个校正子所需的校正量,

具体的实现过程如图6所示。

图 6 FOFB 算法的流水线实现 Fig. 6 Pipeline implementation of FOFB algorithm

在每次FOFB计算周期中,待接收到触发脉冲信号进入T1阶段,等待FOC接收到全环所有BPM的束流位置数据,解码数据帧后将无误码的数据保存在BRAM中的确定地址中。T1阶段的等待时间需要根据在HEPS中的数据传输延时自行设定,待T1阶段结束则进入T2阶段,实时读取BRAM对应地址中的数据完成1152路的增量式PID运算,使用增量式PID运算可以尽可能减少某个BPM数据帧误码对计算结果的影响,同时也可以抑制一定频率范围内的束流轨道扰动[16]。随后将进入T3阶段,并行执行两个576×12的矩阵乘法运算后得到X、Y两方向各12个校正子所需的校正量,执行完成后FOFB算法进入等待状态,直到下一个触发脉冲到来。

计算需要的各个参数,包括黄金轨道、PID参数以及两个方向的响应矩阵逆矩阵( $R^{-1}$ )参数,都预先保存在 FPGA 内部或外部的存储器中(BRAM 或DDR),在计算过程中直接调用。上位机通过网络与FOC进行数据通信,通过上位机可以随时更新FOFB 算法的各个参数,同时也可以获取到束流位置数据、校正量计算结果、电源工作状态等信息,以便于在上位机中完成数据的分析、显示和系统故障诊断等功能。

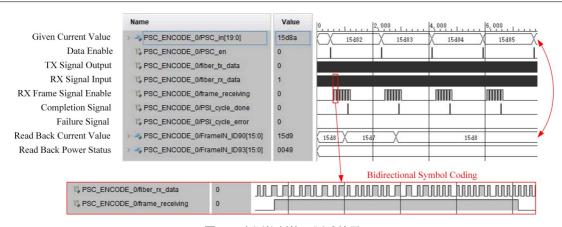

### 2.5 电源控制接口

在FOFB系统中通过电源控制接口实现FOC与PSC的通信,基于数据率、功耗等多方面因素考虑,在HEPS中将使用HFBR-1414作为电源控制接口的发送端,AFBR-2418作为接收端,传输速率设定为40 Mb·s<sup>-1</sup>,一路通道所有器件功耗约为0.4 W。

PSC数据编码扇出模块将FOFB算法计算得到的24个电流设定值分为24个完全独立且同步的数据通道,每个通道与一台快校正子电源连接。在每个通道中,首先将电流设定值、功能码、CRC校验码

编码为新的数据帧,之后将数据帧通过双向符号编码方式再次编码后发送给PSC,最后由PSC的数据解码模块对数据流进行解码,得到电流设定值后直接作用于负载电源,并通过外部同步信号保证所有的快校正子同时响应。

在每发送一帧数据后,FOC还需要接收PSC返回的回读数据,包括电源状态、电流回采值、电源软硬件版本等,由此可以在与FOC相连的上位机中监控所有的快校正子电源的工作状态。

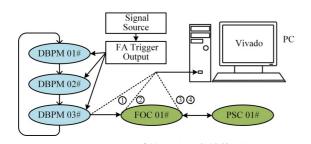

# 3 系统功能测试

在实验室环境下搭建如图7所示的FOFB系统 测试平台,其硬件主要由3套BPM电子学、1套FOC 电子学、1套PSC电子学、信号发生器、FA触发信号 扇出模块、计算机、2 m高速铜缆、50 m多模万兆光 纤以及光模块组成。3套BPM电子学使用高速铜缆 首尾相连组成BPM环路,同时使用外部信号发生器 与FA触发信号扇出模块输出3路22kHz的BPM的 FA 数据触发信号,保证所有 BPM 都在同一时刻发 出FA数据。FOC通过万兆多模光纤与一台BPM相 连,在FOC中完成24路快校正子电流的计算,将其 中一路结果通过光纤传输给后端的PSC,并在每次 传输完成后继续接收PSC发送的回读信号,实时监 测PSC负载电源电流及其他各项参数。整个测试用 于验证FOFB系统数据传输链路的功能并初步估算 链路中的数据传输延时,因此对于各个数据的大小 无具体要求,在测试中BPM不接外部输入信号,使 用基底噪声信号完成测试,且FOFB算法中的各项 参数为自定义测试数据。

在实验中使用 FPGA 内部的集成逻辑分析仪 (Integrated Logic Analyzer, ILA) 执行系统内的调试,通过在计算机 Vivado 软件中设置探针抓取 FPGA 内部的数字信号,实时读取数据链路中的数

图7 FOFB系统测试平台结构图 Fig.7 Structure diagram of FOFB system test platform

据读数,从而验证FOFB系统数据链路中的各个模

块的功能。如图5所示,在整个数据链路中在3个不同位置设置了4个ILA模块,分别用于检验FA位置计算、束流位置传输、FOFB算法以及电源控制接口4个部分的功能。

其中位置1的ILA模块位于BPM的输出端,用于检验FA位置计算功能。测试结果如图8所示,包含4个通道的数字信号处理结果输出、32位的X、Y两个方向的束流位置计算结果以及编码后的64位数据帧。

|             | Name                                              | Value        | 0                | 2,000            |

|-------------|---------------------------------------------------|--------------|------------------|------------------|

| $FA_X$      | > 🚜 system_i/FOFB_GTX/Position_XY_0_YOUT[31:0]    | 00024e95     | 00029b4b         | 00024e95         |

| $FA_Y$      | > 🚜 system_i/FOFB_GTX/Position_XY_0_XOUT[31:0]    | fffec506     | fffeb25b         | fffec506         |

| Channel D   | > 🚜 system_i/FOFB_GTX/FAet_0_FA_DATA_D[31:0]      | 1600         | 1606             | 1600             |

| Channel C   | > 🚜 system_i/FOFB_GTX/FAet_0_FA_DATA_C[31:0]      | 1618         | 1613             | 1618             |

| Channel B   | > 🚜 system_i/FOFB_GTX/FAet_0_FA_DATA_B[31:0]      | 1691         | 1709             | 1691             |

| Channel A   | > 🚜 system_i/FOFB_GTX/FAet_0_FA_DATA_A[31:0]      | 1647         | 1649             | 1647             |

| ncoded Data | > 🚜 system_i/FOFB_GTX/gtx_egtx_data_64bit_1[63:0] | 300007d8a0c2 | 300007d64b629b4b | 300007d8a0c24e95 |

图 8 FA 位置计算测试结果 Fig.8 Calculation result of FA position

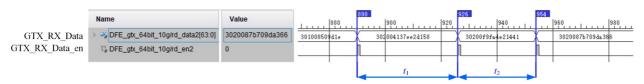

位置2的ILA模块位于FOC的输入端,用于检验束流位置传输功能,在每次BPM接收到FA触发信号之后,FOC都会先后接收到BPM03、BPM02、BPM01的束流位置数据,测试结果如图9所示。图中 $t_2$ 为BPM01的数据传输到BPM02所需的时间, $t_1$ 为BPM02的数据传输到BPM03所需的时间与数据

通过一级接收转发模块的时间之和,因此,可以用 $t_2$ 表示数据通过一级 BPM-BPM 通道的延迟,如图所示需要 28个时钟沿,约为  $0.28~\mu s$ 。 将连接 BPM 的高速铜缆替换为 50~m 多模万兆光纤,使用类似方法可以测得数据通过一级 BPM-FOC 通道或一级 FOC-FOC 通道的延时均为  $0.48~\mu s$ 。

图9 束流位置传输测试结果 Fig.9 Test result of beam position transmission

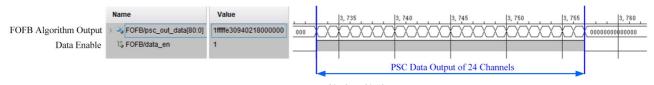

位置3的ILA模块位于FOC的输出端,用于检验FOFB算法的计算结果,如图10所示,计算得到了24路校正子电源的电流设定值结果。同时FOFB算

法由 FOC 外部的 100 MHz 时钟驱动,完成一次 FOFB 需要 700 个时钟沿,即 7  $\mu$ s。

图 10 FOFB 算法计算结果 Fig.10 Calculation result of FOFB algorithm

位置4的ILA模块同样位于FOC的输出端,用于验证电源控制接口部分的功能。测试结果如图11所示,将FOFB算法计算得到的结果截断为20位电流给定值输入,编码为数据帧后通过双向符号编码方式再次编码后发送给PSC。同时在每次发送完数据后继续接收回读数据,可接收的数据包括回读

电流、电源状态、电源软硬件版本等,如图11所示接收到的回读电流数据与给定电流相差不大。同时,由于电源控制接口中主机和从机的程序具有对称性,因此数据从FOC传输到PSC的延迟约为从开始发送数据帧到接收完第一帧回读数据所需时间的一半,约为1.5 μs。

图 11 电源控制接口测试结果 Fig.11 Test result of power control interface

上述测试结果可以验证基于双层环形网络的数据传输链路功能,同时也通过设计 Matlab 仿真与 Vivado Isim 仿真作为三方对照,验证数据链路中各部分计算结果的正确性。整个测试平台可以作为一个局部的 FOFB 系统用于实现局部的束流闭轨校正。

# 4 延迟时间分析

系统延迟时间是FOFB系统的核心指标之一,

是指从BPM探头接收到束流信号开始到快校正子电源完成响应之间的延时,将直接决定整个系统的有效反馈带宽。因此,为了保证系统的有效反馈带宽不低于500 Hz,HEPS 要求系统的总延迟时间应小于160 μs。

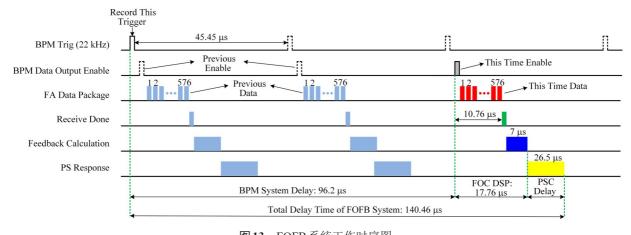

基于双层环形网络的数据传输链路,将FOFB系统的反馈系统总延时分为8部分,依据之前的测试结论,分析FOFB系统每一部分的延时,从而估算HEPS的总延迟时间,如图12所示。

图 12 FOFB 系统延迟时间说明 Fig.12 Illustration of FOFB system delay time

图  $12 + T_1$ 是 BPM 探头到 BPM 电子学输入的信号传输延时,若在 HEPS 中使用 50 m 长的 BPM 线缆,信号在线缆上的传输时间  $T_1$ 约为 0.2 µs。

$T_2$ 定义为BPM接收到首圈信号到发出FA数据的时间间隔。具体包含数据获取等待时间45  $\mu$ s,数据处理时间50  $\mu$ s,FA位置计算及编码输出延迟1 $\mu$ s,因此 $T_2$ 约为96 $\mu$ s。

$T_3$ 、 $T_4$ 、 $T_5$ 分别是 BPM 环路、BPM 到 FOC 和 FOC 环路中的束流位置数据的传输时间。由于在每次控制周期中,任意一个 FOC 都需要接收到全环所有的

BPM 数据后才开始进行计算,因此将束流位置传输总时间定义为从BPM 发出 FA 数据到 FOC 接收到最后一个BPM 数据之间的时间间隔,即一个数据帧先后经过 11 级 BPM-BPM 通道、13 级 BPM-FOC 通道、15 级 FOC-FOC 通道所需的时间。经实验室初步测量,BPM-BPM 的数据传输时间约为  $0.28~\mu s$ ,BPM-FOC 通道和 FOC-FOC 通道的数据传输时间约为  $0.48~\mu s$ 。同时,作为 FOC 最后接收到的数据帧,可以基本忽略其在数据链路中的延迟等待时间。因此束流位置传输总时间  $T_3+T_4+T_5$ 约为  $10.76~\mu s$ 。

$T_6$ 是 FOC 中完成 FOFB 算法的延时,具体定义为从接收到所有 BPM 数据到输出电流给定值之间的时间间隔。当前在 FOC 中完成所一次 FOFB 算法大约需要 700 个时钟沿,当 FOFB 算法的驱动时钟为 100 MHz时,FOFB 算法延时  $T_6$ 约为 7  $\mu$ s。

$T_7$ 是 FOC 到 PSC 的数据传输时间,经实验室测量 $T_7$ 约为  $1.5 \mu s$ 。

$T_{\rm s}$ 定义为从PSC接收到电流给定值到快校正磁铁磁场开始变化的延迟时间,约为25  $\mu$ s。

因此当前结构下的FOFB系统总延迟时间 $T_{total}$

约为:

$$T_{\text{total}} = T_1 + T_2 + T_3 + T_4 + T_5 + T_6 + T_7 + T_8$$

= 140.46 \text{ \text{ } \tex

基于上述分析,绘制HEPS中FOFB系统的工作时序图(图13)。其中,在FOC中的延迟时间为17.76 μs,小于FOFB系统的反馈周期45.45 μs,可以避免在FOC中产生数据混叠,同时也满足FOFB系统总延迟时间小于160 μs 的要求,由此初步验证了当前网络拓扑结构下FOFB系统的可行性。

图13 FOFB系统工作时序图 Fig.13 FOFB system sequence diagram

# 5 结语

基于现有的硬件条件,本文根据HEPS的FOFB系统的有效反馈带宽需求,提出了一种双层环路式的FOFB系统网络拓扑结构,同时介绍了基于该结构的数据传输链路设计方案,并搭建测试平台验证系统的数据传输链路功能。测量和分析结果表明,FOFB系统的数据传输链路中各个功能模块都可以正常使用,且系统总延迟时间约为140.46 µs,已达到预定的设计目标。

FOFB系统是HEPS能否达到预期束流轨道稳定性的关键一环,设计难度大,指标要求高。在本文中设计的FOFB系统双层环形网络结构以及相应的数据传输链路设计方案,一方面为未来FOFB系统在HEPS储存环上的搭建、优化和调试打下了基础,另一方面凭借其良好的灵活性和可拓展性,为将来在其他储存环中通过束流的快速闭轨校正提升性能提供了可行方案。

作者贡献声明 高国栋负责研究的提出及设计,实验验证,数据的收集和整理,文章的起草和最终版本的修订;刘鹏参与酝酿和设计实验,参与实验验证,

对文章的知识性内容作批评性审阅,提供系统所需 软硬件及技术支持;龙锋利参与酝酿和设计实验,对 文章的知识性内容作批评性审阅,行政、技术或材料 支持,提供系统所需软硬件及技术支持;季大恒参与 酝酿和设计实验,数据统计分析,行政、技术或材料 支持;叶强参与酝酿和设计实验,行政、技术或材料 支持,指导及支持性贡献;杜垚垚提供研究经费,对 文章的知识性内容作批评性审阅,行政、技术或硬件 材料支持,提供系统所需软硬件及技术支持;刘智对 文章的知识性内容作批评性审阅,行政、技术或硬件 材料支持,提供系统所需软硬件及技术支持;随艳峰 获取研究经费,行政、技术或材料支持,指导及支持 性贡献;岳军会获取研究经费,行政、技术或材料支 持,指导及支持性贡献;唐旭辉参与实验验证,参与 系统的前期设计工作,提供部分技术支持;魏书军负 责项目的监督和管理,酝酿和设计实验,对文章的知 识性内容作批评性审阅,行政、技术或材料支持,指 导及支持性贡献;曹建社负责项目的监督和管理,酝 酿和设计实验,对文章的知识性内容作批评性审阅, 行政、技术或材料支持,指导及支持性贡献。

# 参考文献

- 1 姜晓明, 王九庆, 秦庆, 等. 中国高能同步辐射光源及其验证装置工程[J]. 中国科学: 物理学 力学 天文学, 2014, 44(10): 1075 1094. DOI: 10.1360/SSPMA2014-00158. JIANG Xiaoming, WANG Jiuqing, QIN Qing, et al. Chinese high energy photon source and the test facility[J]. Scientia Sinica (Physica, Mechanica & Astronomica), 2014, 44(10): 1075 1094. DOI: 10.1360/SSPMA2014-00158.

- 2 中国科学院高能物理研究所. HEPS 初步设计报告[R]. 北京: 中国科学院高能物理研究所, 2015. Institute of High Energy Physics, Chinese Academy of Sciences. HEPS preliminary design report[R]. Beijing: Institute of High Energy Physics, Chinese Academy of Sciences, 2015.

- 3 殷重先, 赵黎颖, 姜伯承. 上海光源快速轨道反馈系统 [J]. 原子能科学技术, 2015, **49**(S2): 615 619. DOI: 10. 7538/yzk.2015.49.S1.0615.

- YIN Chongxian, ZHAO Liying, JIANG Bocheng. Shanghai synchrotron radiation facility fast obit feedback system[J]. Atomic Energy Science and Technology, 2015, 49(S2): 615 619. DOI: 10.7538/yzk.2015.49.S1.0615.

- 4 Chiu P C, Cheng Y S, Hsu K T, et al. Status of the fast orbit feedback system for the TPS[C]. Proceedings of ICALEPCS2017, Barcelona, Spain. 2017.

- 5 Uzun I S, Heron M T. Diamond light source fast orbit feedback communication controller specification and design[R]. Diamond Light Source Ltd, Rutherford Appleton Laboratory, 2007.

- 6 Tian Y, Ha K, Yu L, et al. NSLS-II fast orbit feedback system[C]. Proceedings of ICALEPCS 2015, Melbourne, Australia. 2015.

- 7 Kallakuri P, Paskvan D, Carwardine J, et al. Modeling the fast orbit feedback control system for APS upgrade[C]. Proceedings of IBIC 2017, MI, USA. 2017.

- 8 Tavares D. BPM electronics and orbit feedback systems at sirius[R]. LNLS Beam Diagnostics Group, 2018.

- 9 随艳峰, 杜垚垚, 叶强, 等. 基于BEPCII数字束流位置测量系统电子学系统的设计与实现[J]. 原子能科学技术, 2020, **54**(1): 172 178. DOI: 10.7538/yzk.2019.youxian. 0044.

- SUI Yanfeng, DU Yaoyao, YE Qiang, *et al.* Development of digital beam position monitor electronics system based on BEPC II [J]. Atomic Energy Science and Technology, 2020, **54**(1): 172 178. DOI: 10.7538/yzk.2019.youxian.

### 0044.

- 10 刘鹏, 龙锋利, 李洋, 等. 高能同步辐射光源储存环快校 正磁铁电源设计[J]. 原子能科学技术, 2020, **54**(11): 2252 - 2257.

- LIU Peng, LONG Fengli, LI Yang, *et al.* Design of fast corrector magnet power supply for HEPS storage ring[J]. Atomic Energy Science and Technology, 2020, **54**(11): 2252 2257.

- 11 高国栋, 唐旭辉, 曹建社, 等. 数字束流位置探测器系统的信噪比需求分析[J]. 强激光与粒子束, 2022, **34**(6): 56 63. DOI: 10.11884/HPLPB202234.210522.

- GAO Guodong, TANG Xuhui, CAO Jianshe, *et al.* Signal-to-noise ratio requirement analysis for digital beam position monitor system[J]. High Power Laser and Particle Beams, 2022, **34**(6): 56 63. DOI: 10.11884/HPLPB202234.210522.

- 12 Du Y Y, Yang J, Wang L, *et al.* Design of RF front end of digital BPM for BEPCII[J]. Radiation Detection Technology and Methods, 2019, **3**(3): 38. DOI: 10.1007/s41605-019-0119-x.

- 13 马宇飞, 周嘉申, 曹建社, 等. 基于 BEPC II的数字束流位置探测器信号处理算法的 FPGA 实现[J]. 原子能科学技术, 2018, **52**(10): 1874 1878. DOI: 10.7538/yzk.2018. youxian.0093.

- MA Yufei, ZHOU Jiashen, CAO Jianshe, *et al.* Implementation of digital beam position monitor signal processing algorithm in FPGA based on BEPC II [J]. Atomic Energy Science and Technology, 2018, **52**(10): 1874 1878. DOI: 10.7538/yzk.2018.youxian.0093.

- 14 靳蕴瑜. 基于 FPGA 的高速数据互连模块设计与应用 [D]. 成都: 电子科技大学, 2018.

- JIN Wenyu. Design and application of high-speed data interconnection module based on FPGA[D]. Chengdu: University of Electronic Science and Technology of China, 2018.

- 5 李亮. 基于 FPGA 的高速光纤通信数据传输技术的研究与实现[D]. 长春: 吉林大学, 2017.

- LI Liang. Research and implementation of high-speed optical fiber communication data transmission technology based on FPGA[D]. Changehun: Jilin University, 2017.

- 16 殷重先. SSRF快速轨道反馈系统研究[D]. 上海: 中国科学院上海应用物理研究所, 2007.

- YIN Chongxian. Research on SSRF fast track feedback system[D]. Shanghai: Shanghai Institute of Applied Physics, Chinese Academy of Sciences, 2007.