**REVIEWS**

## **Trending IC design directions in 2022**

Chi-Hang Chan<sup>1</sup>, Lin Cheng<sup>2</sup>, Wei Deng<sup>3</sup>, Peng Feng<sup>4</sup>, Li Geng<sup>5</sup>, Mo Huang<sup>1</sup>, Haikun Jia<sup>3</sup>, Lu Jie<sup>3</sup>, Ka-Meng Lei<sup>1</sup>, Xihao Liu<sup>5</sup>, Xun Liu<sup>6</sup>, Yongpan Liu<sup>3</sup>, Yan Lu<sup>1, †</sup>, Kaiming Nie<sup>7</sup>, Dongfang Pan<sup>2</sup>, Nan Qi<sup>4</sup>, Sai-Weng Sin<sup>1</sup>, Nan Sun<sup>3</sup>, Wenyu Sun<sup>3</sup>, Jiangtao Xu<sup>7</sup>, Jinshan Yue<sup>3</sup>, Milin Zhang<sup>3</sup>, and Zhao Zhang<sup>4</sup>

<sup>1</sup>University of Macau, Macau 999078, China <sup>2</sup>University of Science and Technology of China, Hefei 230026, China <sup>3</sup>Tsinghua University, Beijing 100084, China <sup>4</sup>Institute of Semiconductors, Chinese Academy of Sciences, Beijing 100083, China <sup>5</sup>Xi'an Jiaotong University, Xi'an 710049, China <sup>6</sup>Chinese University of Hong Kong, Shenzhen 518172, China <sup>7</sup>Tianjin University, Tianjin 300072, China All the Authors contribute equally to this paper, names are listed in alphabetical order.

**Abstract:** For the non-stop demands for a better and smarter society, the number of electronic devices keeps increasing exponentially; and the computation power, communication data rate, smart sensing capability and intelligence are always not enough. Hardware supports software, while the integrated circuit (IC) is the core of hardware. In this long review paper, we summarize and discuss recent trending IC design directions and challenges, and try to give the readers big/cool pictures on each selected small/hot topics. We divide the trends into the following six categories, namely, 1) machine learning and artificial intelligence (AI) chips, 2) communication ICs, 3) data converters, 4) power converters, 5) imagers and range sensors, 6) emerging directions. Hope you find this paper useful for your future research and works.

Key words: integrated circuit design; artificial intelligence (AI); radio frequency (RF) circuits; data converters; power management; imager; sensor; cryogenic; biomedical

**Citation:** C H Chan, L Cheng, W Deng, P Feng, L Geng, M Huang, H K Jia, L Jie, K M Lei, X H Liu, X Liu, Y P Liu, Y Lu, K M Nie, D F Pan, N Qi, S W Sin, N Sun, W Y Sun, J T Xu, J S Yue, M L Zhang, and Z Zhang, Trending IC design directions in 2022[J]. *J. Semicond.*, 2022, 43(7), 071401. https://doi.org/10.1088/1674-4926/43/7/071401

## 1. Background

With the emerging applications of artificial intelligence (AI), big data, blockchain, internet-of-things (IoT), autonomous driving, drones/robots, metaverse, etc., and also due to the CoVid-19 pandemic makes people working from home and pushes the companies to setup a blended work model with distributed workforce, the demand for integrated circuits (IC) chips sees an explosive growth in recent two years. Needless to say, a tremendous amount of new circuit design challenges appears along with these new applications. Cutting-edge technologies and circuit innovations are the enablers for satisfying the ever-increasing circuit performance specifications, in terms of data rate, precision, resolution, percep-

Correspondence to: Y Lu, yanlu@um.edu.mo

Received 30 MARCH 2022; Revised 23 APRIL 2022.

©2022 Chinese Institute of Electronics

tion capability, intelligence level, and energy efficiency.

China (the Far-East of the world), as the largest consumer of IC chips in the world, strategically focuses on not only the network infrastructures and the terminal equipment, but also the core hardware component — the chip. Driven by the new waves of technology, both the IC design industry and academia in China are catching up. In particular, it seems that the academia goes a little bit faster, as we can find from the data of the number of published papers on the IEEE International Solid-State Circuits Conference (ISSCC) and the Journal of Solid-State Circuits (JSSC), which are the topmost conference and journal in the field of IC design, respectively. Here in this review paper, we invite the active authors from China to provide their humble opinions on the recent trending IC design directions in 2022.

The following contents are categorized into six sections. Section 2 on machine learning and AI chips introduces AI chips for domain-specific applications, and emerging compute-in-memory circuits. Section 3 on communications IC discusses wireless/wireline transceivers, power amplifiers (PAs), clock generators and frequency synthesizers. Section 4 on analog-to-digital (ADC) data converters covers recent promising hybrid ADC architectures, and high-resolution ADCs. Section 5 on integrated power converters focuses on the topology and controller design of switched-inductor-capacitor hybrid power converters, isolated power, and the supply modulator

All the reviewers who gave comments on this paper are acknowledged, and their names are listed as follows: Zhiyuan Chen and Zhiliang Hong are with Fudan University, China; Qiang Li, Jiaxin Liu, and Xun Luo are with University of Electronic Science and Technology of China, China; Fujiang Lin is with University of Science and Technology of China, China; Liyuan Liu and Nanjian Wu are with Institute of Semiconductors, Chinese Academy of Sciences, China; Man-Kay Law, Pui-In Elvis Mak, and Ka-Fai Un are with University of Macau, China; Jun Yang and Dixian Zhao are with Southeast University, China.

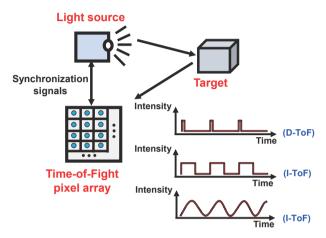

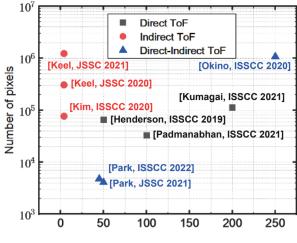

for PA in 5G communication. Section 6 on CMOS imagers and range sensors talks about event-based and high dynamic range image sensors, as well as the time-of-flight (ToF) range sensors. Last but not least, Section 7 on emerging directions leads us to the cryogenic CMOS for qubit and biomedical frontiers. Finally, we draw conclusions in Section 8.

# 2. Machine learning and artificial intelligence chips

When people nowadays are working towards to metaverse or the "Matrix", the first trending direction has to be Al chips. Besides the conventional general Al computer systems, custom processors are becoming more ubiquitous in the machine learning space, motivating the chip design for domainspecific applications, which include voice, image, and some other emerging directions. Meanwhile, computing-inmemory chips, at both the macro-level and system-level, have become an important technical approach for energy-efficient or high-performance Al chips.

## 2.1. Al chips for domain-specific applications

Custom processors are becoming more ubiquitous in the machine learning (ML) space, motivating the chip design for domain-specific applications (DSA). Through the methodology of hardware-software co-optimization, the DSA chips can bring a great leap of performance for target applications. Reviewing the ISSCC publications in recent three years, Al chips for DSA have drawn extensive attention for various applications, including voice, image, and some other emerging directions.

## 2.1.1. AI chips for voice applications

For voice applications, keyword spotting (KWS) and automatic speech recognition (ASR) can be widely applied to various wearable or mobile devices. For such battery-powered applications, ultra-low power is a strong requirement for voice processing chips. Typically, a KWS or ASR system is composed by the feature extractor and the AI signal processing, and recent works aims at optimizing the power of such two modules in circuit and system level.

Shan<sup>[1]</sup> implements a sub- $\mu$ W KWS chip in ISSCC'20, aiming for 1–2 keywords spotting. To extract the voice feature of mel frequency cepstrum coefficient (MFCC), they designed a specific serial-pipeline fast fourier transformation (FFT) circuit with compressed on-chip memory. In AI processing, the depthwise-separable CNN is adopted with binarized activations, which reduces the storage and computation by 7× compared with normal CNN model. Different from traditional method to use the whole word for KWS, they eliminate the redundant computations and data storage coming from similar adjacent inputs. As a result, the chip achieves 94.6% accuracy for two-word spotting with only 0.51  $\mu$ W power and 2 KB onchip memory.

Although the chip in Ref. [1] achieves ultra-low-power (ULP) consumption, it adopts the noise-dependent training so the accuracy will degrade in low signal-to-noise (SNR) level. To achieve high robustness KWS, one method is to include all the possible SNR levels and noise types in the AI model training, which causes the increasing of model size and is challenging for ultra-low-power applications. To overcome the noise problem in KWS, Wang<sup>[2]</sup> employed a simpler voice extracting method called divisive energy normalization (DN),

and developed a normalized acoustic feature extractor chip (NAFE) for analog signal processing. The frontend of NAFE is composed by a low-noise amplifier (LNA), a bandpass filter (BFP), a half-wave rectifier (HWR) and an integrate-and-fire (IAF) encoder, and extract the pre-normalized features (preNF). Then, the DN model is performed in preNF to estimate the background noise level by converting background noise to white noise, and produces post-normalized features (postNF). In AI signal processing, they use a well-developed spiking neural network (SNN) classifier chip and combine it with NAFE to realize an end-to-end KWS. The overall KWS system is robust for noisy condition and achieves an average accuracy of 92.8% in different SNR level.

Different from KWS that only needs to implement smallvocabulary tasks (1-2 words), ASR has to deal with large-vocabular tasks of more than 10<sup>5</sup> words. As a result, models with bidirectional recurrent neural network (RNN) and attention mechanism are necessary for improving the ASR accuracy. To accelerating ASR, Tambe<sup>[3]</sup> presents a 16-nm SoC that executes a full speech-enhancing pipeline in ISSCC'21. The chip is composed by a markov source separation engine (MSSE), for feature extracting, an Arm Cortex-A53 CPU for signal pre-processing, and a reconfigurable accelerator (FlexASR) for AI processing. In feature extractor, the MSSE uses bayesian algorithm and can make a binary label to distinguish noise and speech, which realize unsupervised speech denoising. Then the FlexASR, which comprises 4 processing elements and a multi-function global buffer, works to accelerate the bidirectional attention-based speech-to-text model. It supports most of the operations in seq2seq models, such as attention mechanism, mean/max pooling, and normalization. For attention computing, FlexASR is optimized to gate and skip computations in null states. The chip can achieve 2.25 mJ of energy per frame with real-time 18 ms latency, and is the first to demonstrate on-chip support for denoised, large-vocabulary ASR for bidirectional attention-based speech recognition.

To further reduce the power for IoT platforms, the technology of voice activity detection (VAD) that can gain attention on events-of-interest and is becoming an interesting topic. In such system, the always-on acoustic wakeup detector dominates the overall power consumption since the remainder of the VAD system is power-gated during sleeping time. As a result, an ultra-low-power and wide bandwidth feature extractor with wakeup detection is more important for VAD. Although achieves  $\mu$ W-level power, traditional analog-domain feature extraction-based VADs often adopt a simple decision tree or a fixed neural network for detection, and can only be applied to limited acoustic event targets. In ISSCC'19, Cho<sup>[4]</sup> adopts the time-interleaved mixer-based architecture to present a neural network NN-based acoustic sensing system for both VAD and non-voice event detection. In analog frontend, it has two signal chains: a 142 nW ULP chain which is always on for wakeup detection, and an 18  $\mu$ W high performance (HP) chain which is used when system is waked up. For the ULP chain, the time-interleaved mixer-based architecture sequentially scans and down-converts the 4 kHz bandwidth signal to less than 500 Hz passband, which reduce the power consumption of amplifier, ADC and DSP by 4 times. In the digital backend, the power optimization of leakage power is important for the always on circuits. In their chip, thick oxide I/O devices are used to implement the always-on modules to suppress the static leakage power. The NN processor adopts a 16 kB custom ultra-low leakage static random-access memory (SRAM) to store the 4-bit weight. In the ULP mode, the processor runs with a small NN every 512 ms when the feature extraction is complete, and at other times it is power-gated to minimize the leakage power. In the HP mode, the processor computes a FFT and a larger NN for improved 32 ms latency. The chip is also integrated with a MEMS microphone and achieves 91.5%/90% speech/non-speech hit rates at 10 dB SNR with babble noise in the ULP mode. Although the work in Ref. [4] achieved an ultra-low power for the feature extractor, the 512-ms decision latency prevents it from real-time VAD applications.

To realize real-time wakeup decision, Chen<sup>[5]</sup> adopts the time-domain CNN (TD-CNN) for analog feature extracting in IS-SCC'22. Different from previous analog filter-based frontend, the TD-CNN evaluates the signal from LNA buffers by 1-D convolution layer in a temporal manner. As a part of the AI models, the TD-CNN can be trained with the entire network, which permits reprogramming to adapt for various applications with different characteristics. The TD-CNN is realized by an analog circuit with a switched-capacitor (SC) array and adopts a 3-bit sparsified quantization scheme, which shows an accuracy higher than 7-bit binary quantization. After the TD-CNN pre-processing, the extracted features can be concatenated into a 2-D feature map and be further processed for more complex tasks. Compared with Ref. [4], it achieves 50 times higher framerate with similar power budget.

## 2.1.2. Al chips for image or video processing

For image or video processing, people paid more attentions to improve the energy and frame efficiency for executing the AI models, with the co-optimization technology of algorithm and architecture, low-bit model quantization and sparse model acceleration.

Lu<sup>[6]</sup> proposes a low-power and real-time vision-based hand-gesture recognition (HGR) system in ISSCC'21. The overall architecture is mainly composed by a pre-processing unit, a recognition core and a sequence analyzer (SA). First, the pre-processing unit helps to segment the hand region from color image. Second, a motion detection unit, a hand localization unit, and a feature extraction unit in the recognition core work together to generate the input feature data for two customized classifiers: the edge-CNN core (ECCNC) and the decision tree core (DTC). Finally, the SA integrates the decision of ECNNC and DTC to improve the accuracy and robustness of HGR system. To optimize the computing efficiency, this work explores the data reuse space of ECCNC. The 2-layer edge-CNN model shows a 32× space of weight reusing for the first layer and a  $6 \times$  space of feature reuse for both layers. To maximize the data reusing, ECCNC employs the sharedlink connection between multiple PEs so that the feature and weight data can be reused by different PEs. Such flexible data scheduling reduces 27% memory access. Besides the ECCNC, the DTC works to improve the system's error tolerance. The SA analyzes the results from ECCNC and DTC to judge the specific gesture type, and helps the system to achieve 92.6% accuracy and 30-fps real-time recognition with only  $184-\mu W$ power consumption.

Im<sup>[7]</sup> aims at accelerating the depth image processing for 3D bounding box extraction, and propose the depth signal processing unit (DSPU) in ISSCC'22. The overall flow for 3D extraction includes many modules, such as depth CNN, neighbor search, point sampling (UDS), point grouping (BQ), and point CNN. To reduce the area overhead, DSPU develop a unified matrix-processing unit (UMPU) and a unified point-processing unit (UPPU), where all matrix computations are shared in the UMPU and all point operations are shared in the UUPU. Since the point NN has high sparse input features, the DSPU adopts slice-level-skipping PE for zero input skip. To reduce the redundant computation caused by the max polling layer, the largest values are predicted by 4-b MSB convolution of inputs and weights to skip the non-maximal outputs. By the optimization of sparse acceleration, the total latency of PNN can be reduced by 44.5%. As a result, the DSPU finally achieves 31.9-fps with 281.6-mW to realize endto-end RGB-D acquisition and 3D BB extraction.

Compared with image data, video has one more dimension of time and provides more design space in algorithm and hardware. Since adjacent frames share similar information, efficiently leverage video temporal correlations to minimize the computing costs for video model is worth exploring. In ISSCC'20, Yuan<sup>[8]</sup> proposes an inter-frame data-reuse processors for video accelerating. Other than directly inputting the original frames, the work processes the difference feature between two frames in each CNN layer to reduce the redundant computation. The work finds that although typical frames in a period of time are similar, it does not mean they are identical and the diff-feature has limited sparsity. In order to process diff-feature without accuracy loss while improving the computing efficiency, the chip adopts a hybrid-precision inter-frame data-reuse scheme. In hybrid precision coding, low precision 4-b tensor is adopted for relatively small values in the feature map, while 8-b sparse tensor is adopted for the others. The two tensors have separate storages with multiple-type sparse coding methods. With inter-frame data reuse, the off-chip data transmission is significantly reduced by 15%–30% for different datasets. Finally, the 65-nm chip can reduce up to 76.3% power to achieve a 24.7-µJ per frame energy efficiency.

For emerging AI models, transformers have achieved great success in multiple AI fields, from natural language processing (NLP) to computer vision. Compared with CNN models, transformer calls for larger memory storage and different data reusing mechanism. To develop specific architecture for transformer accelerating, two relative chips are presented in IS-SCC'22. Wang<sup>[9]</sup> presents a digital transformer processor to achieve 27.5 TOPS/W energy efficiency by asymptotic sparsity speculating. This work find that the transformer model contains many weakly related tokens with small scores caused by the attention operation. Such weak tokens can take up to 93.1% energy consumption in the whole system, but has limited influence on the model accuracy. Moreover, the softmax function results in many zero data, but the sparsity is irregular and hard to predict. To overcome such problems, the work adopts a big-exact-small-approximate (BESA) PE to gate the computation of LSBs for small values, which saves 1.62× MAC power. To skip the sparse computing, a bidirectional asymptotic speculation unit (BASU) is designed to explore the attention's local properties and exploit the presence of sparsity, which skips 46.7% of the redundant computations. The 28-nm chip uses 27.56 TOPS/W peak energy efficiency to implement the transformer model.

|                     |                            | ISSCC'20, 14.1, [1] | ISSCC'21, 9.9, [2]       | ISSCC'21, 9.8, [3]         |

|---------------------|----------------------------|---------------------|--------------------------|----------------------------|

|                     | Technology (nm)            | 28                  | 90                       | 16                         |

|                     | Model                      | DSCNN               | DT                       | RNN                        |

|                     | Memory                     | 2 KB                | -                        | 9.8 MB                     |

| Speech (KWS/ASR)    | Latency (ms)               | 64                  | <100                     | 15–45                      |

|                     | Power (µW)                 | 0.51                | 6                        | 1.11 × 10 <sup>5</sup>     |

|                     | Word                       | 1–2                 | 1                        | $2 \times 10^{5}$          |

|                     | Denoising                  | No                  | Yes                      | Yes                        |

|                     |                            | ISSCC'19, 17.2, [4] | ISSCC'22, 22.5, [5]      |                            |

|                     | Technology (nm)            | 180                 | 28                       |                            |

|                     | Feature type               | Mixed-signal        | TD-CNN                   |                            |

|                     | Channel number             | 16–48               | 60                       |                            |

| Speech (VAD)        | Freq. range (Hz)           | 75–4000             | 100–4000                 |                            |

|                     | VAD power (nW)             | 142                 | 108                      |                            |

|                     | VAD accuracy               | 90% @ nonspeech     | 94% @ nonspeech          |                            |

|                     | Energy/Classification (nJ) | 73                  | 1.08                     |                            |

|                     |                            | ISSCC'21, 9.7, [6]  | ISSCC'22, 33.4, [7]      | ISSCC'20, 14.2, [8]        |

|                     | Technology (nm)            | 65                  | 65                       | 65                         |

| 0 <i>1</i> - 1      | Model                      | Edge CNN (GTR)      | Point CNN (3D detection) | MobileNet (Classification) |

| mage/Video          | Memory (KB)                | -                   | 364 KB                   | 196 KB                     |

|                     | Power (mW)                 | 0.184               | 544–609                  | 7.3–99                     |

|                     | Frame efficiency           | 30 fps              | 3.2 mJ/Frame             | 24.7–183.2 μJ/Frame        |

|                     |                            | ISSCC'22, 29.2, [9] | ISSCC'22, 29.3, [10]     |                            |

|                     | Technology (nm)            | 28                  | 28                       |                            |

| Emoraina directions | App.                       | Transformer         | Transformer              |                            |

| Emerging directions | Memory (KB)                | 336                 | 192                      |                            |

|                     | Energy efficiency (TOPS/W) | 1.91–27.56          | 5.1–20.5                 |                            |

|                     | Power (mW)                 | 12–272              | 27–118                   |                            |

Table 1. Performance summary of AI chips for different DSA.

Also in this year, Tu<sup>[10]</sup> proposes a transformer accelerator TranCIM, but based on computing-in-memory (CIM) architecture. Different from static model, the online generated weights and inputs of attention layers causes redundant offchip memory access. TransCIM employs a CIM pipeline architecture combined with the bitline-transpose structure to align the directions of input and weight feeding, and allow intermediate data to stream from the first engine to the next. The CIM chip was fabricated in 28-nm CMOS and achieves a 20.5 TOPS/W energy efficiency for INT8 computing.

The DSA chips mentioned above mainly follow the road of algorithm-architecture co-optimization. Aiming at one specific applications, they analyze the demand and develop the high-efficiency analog or digital circuits. Inspired by 2.5D/3D stacked integrating technologies for high bandwidth memory fabrication, the road of monolithic 3D and hybrid bonding techniques are also explored for DSA chips. Eki<sup>[11]</sup> from Sony presents a stacked CMOS image sensor (CIS) with Al computing ability. The CIS block for sensor is integrated with a digital signal processor (DSP) for CNN computing together through 3D stacking in this work. The top CIS chip is fabricated in a 65-nm process while bottom DSP chip is using a 22-nm process, which shows an attractive solution for intelligent and low-cost vision sensor.

Niu<sup>[12]</sup> stacks a 25-nm dynamic random-access memory (DRAM) die on top of a 55-nm logic die and gives a nearmemory-processing solution for the memory-bound recommendation system. The chip achieves a 307 bandwidth-to-capacity ratio and 0.88 pJ/b energy cost, which outperforms the prior processing-near-memory chips significantly because of the hybrid bonding scheme. It is foreseeable that more DSA chips using monolithic 3D and hybrid bonding technologies (sensor-logic stacking, memory-logic stacking, logic-logic stacking ...) will be explored to increase the data transmission speed and efficiency.

Based on the reviews above, we can see that significant progresses have been made in machine learning processor design for specific application acceleration. Table 1 gathers the performances for DSA chips appeared in recent three years of ISSCC. One important trend of DSA processor is designing the computing and storage architectures to match with the specific application's characteristics. Algorithm-architecture co-optimization is adopted by researchers to explore the design space of low-bit quantization, sparse computation, dedicated circuit, and so on. The KWS chips used in wearable devices calls for low-memory hardware architecture and low-complexity AI models to reduce power. Moreover, the problem of background noise needs to be properly solved to improve the speech system's robustness. Thus, analog single processing circuit and unsupervised speech algorithms are under research for denoising. Image or video processing pays more attention to the frame efficiency, which calls for pipelined and sparse computing optimization. As an emerging direction, transformer processors process different model architectures, necessitating innovations in customized hardware design for the attention mechanism. Another trend is

| Table 2. | Summary | of the SRAM-based CIM macros. |

|----------|---------|-------------------------------|

|----------|---------|-------------------------------|

|                           |                  |               |            |                             | ,                            |                 |                       |                                  |                                            |                                     |

|---------------------------|------------------|---------------|------------|-----------------------------|------------------------------|-----------------|-----------------------|----------------------------------|--------------------------------------------|-------------------------------------|

| Ref.                      | CIM<br>mode      | Tech.<br>(nm) | Macro size | Input<br>precision<br>(bit) | Weight<br>precision<br>(bit) | Output<br>ratio | Performance<br>(TOPS) | Energy<br>efficiency<br>(TOPS/W) | Area efficiency<br>(TOPS/mm <sup>2</sup> ) | Inference<br>accuracy<br>(Cifar-10) |

| [ <mark>13</mark> ], 2020 |                  | 28            | 64 Kb      | 4/8                         | 4/8                          | 1:1             | _                     | 68.44@4b/4b                      | _                                          | 92.02%                              |

| [14], 2020                | Current<br>based | 65            | 16 Kb      | 2/4/6/8                     | 4/8                          | 1:12            | 2.0*@2b/4b            | 16.63@8b/8b<br>158.7*@2b/4b      | 3.38*@2b/4b                                | 91.74%                              |

| [ <mark>15</mark> ], 2021 |                  | 65            | 64 Kb      | 2/4/6/8                     | 1–8                          | 1:1             | 3.16*@2b/1b           | 370*@2b/1b                       | 1.85*@2b/1b                                | 92.65%                              |

| [ <mark>22</mark> ], 2021 | Charge           | 28            | 384 Kb     | 4/8                         | 4/8                          | 1:1             | _                     | 94.31@4b/4b                      | _                                          | _                                   |

| [ <mark>23</mark> ], 2021 | based            | 16            | 4.5 Mb     | 1–8                         | 1–8                          | 1:4.5           | 11.8@4b/4b            | 121@4b/4b                        | 2.67@4b/4b                                 | 91.51%                              |

| [ <mark>16</mark> ], 2021 |                  | 22            | 64 Kb      | 1–8                         | 4/8/12/16                    | 1:1             | 3.3@4b/4b             | 89*@4b/4b                        | 16.3*@4b/4b                                | #                                   |

| [17], 2022                | All-             | 28            | 32 Kb      | 1–8                         | 1/4/8                        | 1:1             | -                     | 27.38@8b/8b                      | -                                          | #                                   |

| [ <mark>20</mark> ], 2022 | digital          | 5             | 64 Kb      | 4                           | 4                            | 1:1             | 2.94@4b/4b            | 254*@4b/4b                       | 221@4b/4b                                  | #                                   |

| [ <mark>21</mark> ], 2022 | -                | 28            | 16 Kb      | 1                           | 1                            | 1:1             | 20@1b/1b              | 2219@1b/1b                       | 606@1b/1b                                  | 86.9%                               |

| [18], 2022                | Time<br>based    | 28            | 1 Mb       | 4/8                         | 4/8                          | 1:1             | 4.96@4b/4b            | 148.1*@4b/4b<br>37.01*@8b/8b     | _                                          | 92.08%                              |

\*: with sparsity improvement or at 10% input toggle rate. @4b/4b: 4bit input, 4bit weight. #: the same accuracy to the software baseline at the same precision.

monolithic 3D and hybrid bonding that stacks different kinds of chips in one system to offer significant bandwidth and power benefits.

## 2.2. Computing-in-memory chips

Computing-in-Memory (CIM) chips have become an important technical approach for energy-efficient or high-performance AI chips. The recent CIM chips mainly focus on two design levels: the macro-level and system-level CIM chips.

## 2.2.1. Macro-level CIM chips

The macro-level CIM chips aim at higher energy efficiency, higher density, better accuracy and higher performance. The current-based, charge-based, all-digital, and timebased CIM macro structures have been proposed. The key design concerns include low-power ADC, high-density CIM cell structure, high accuracy, more functionality, etc.

ADC design is critical for an energy-efficient CIM chip as it occupies the majority of the power consumption. Based on the algorithm analysis, the multiply-accumulate (MAC) values of the ADC input concentrate on low values. Therefore, one reference voltage can be adopted for pre-classification, which reduces the ADC sensing bit of low MAC values<sup>[13]</sup>. The sparsity technique is adopted to pre-train a whole weight block as zero, so that the corresponding ADC result can be determined as zero by the sparsity index<sup>[14]</sup>, which saves the ADC sensing power for zero results. Furthermore, an ADC with flexible bit-precision is designed, where the 2-bit index can dynamically select the 0-/2-/4-bit ADC sensing modes<sup>[15]</sup>. In the all-digital CIM structure that does not need the ADCs, the majority of the power consumption comes from the digital adder tree. The interleaved 14T/28T full adder can increase the energy efficiency by 30%<sup>[16]</sup>. Dynamic logic is also explored for better energy efficiency, which shows no leakage and hazard problems<sup>[17]</sup>. The evolving time-based CIM structure replaces ADC with time-to-digital converter (TDC)<sup>[18, 19]</sup>. By eliminating ADC and adopting the dynamic differentialreference TDC, the time-based CIM structure shows 37.1× and 6.18× higher energy efficiency than the current-based and charge-based CIM structure<sup>[18]</sup>. Besides, the time-space readout can be executed simultaneously to the analog MAC developing operation, which avoids long computing latency due to heavy resistance and capacitance (RC) parameters<sup>[19]</sup>.

Storage density and computation density are also key features for the CIM macro. For higher computation density, several storage cells are grouped together to share the same local-computing-cell for CIM operation<sup>[13]</sup>. The all-digital CIM structure shows better scaling improvement for higher storage/computation density, which achieves 221 TOPS/mm<sup>2</sup> area efficiency at 5-nm technology node<sup>[20]</sup>. Approximate circuits for all-digital CIM structure can reduce the transistor quantity. The double approximate compressor shows 56.4% transistor reduction with 2569 F2/b area efficiency<sup>[21]</sup>.

Accuracy is an important concern for CIM macro design. For better accuracy, the output ratio, which is the ratio of the real output resolution and the ideal output resolution, is a key parameter for current/charge-based CIM structures<sup>[22]</sup>. A higher output ratio improves the accuracy, while requiring higher power consumption. Compared with the current/ charge-based CIM structures that are sensitive to process, voltage, and temperature variations, the all-digital CIM structure shows no analog accuracy loss<sup>[16, 20]</sup>. The charge-based CIM structure shows reasonable accuracy with high parallelism, which can activate 1152 input rows simultaneously<sup>[23]</sup>. The evolving time-based CIM structure presents better accuracy and lower power consumption<sup>[18, 19]</sup>. In each delay computing unit, the MAC operation result is converted to the accumulated time delay between the input and output signals<sup>[18]</sup>, which achieves 8× higher normalized signal margin than the previous voltage-domain ADC based CIM structure.

More functionality is also explored on the CIM macro structures. Several works have explored configurable activation/weight bit-precision, among which the 2's/non-2's com plementary ADC is designed to support signed/unsigned MAC operations<sup>[14]</sup>. To support both inference and training applications, a two-way transpose CIM macro is proposed, which can utilize two directions of CIM operation without weight data transpose operation<sup>[24]</sup>. Table 2 summarizes the key features of the state-of-the-art SRAM-based CIM macros.

## 2.2.2. System-level CIM chips

On the other hand, the system-level CIM chips present more sophisticated CIM architecture with more flexible operator support.

Inter/intra-macro data reuse and channel/kernel-order weight mapping strategies are explored on the CIM architec-

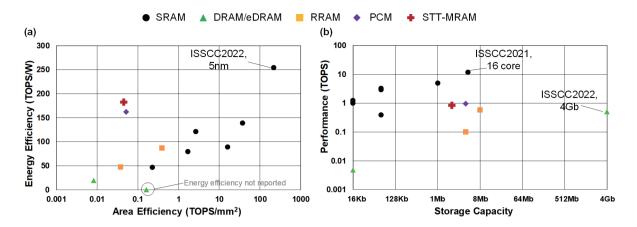

Fig. 1. (Color online) Comparison of the state-of-the-art CIM macros (scaled to 4-bit input, 4-bit weight), with (a) energy efficiency and area efficiency, and (b) performance and storage capacity.

tures for better resource utilization<sup>[14]</sup>. Multi-core CIM systems are designed to extend the CIM performance and functionality. A 16-core CIM system with programmable single instruction multiple data (SIMD) data path and flexible on-chip network shows 96% bit-cell utilization on Cifar-10 dataset<sup>[23]</sup>. To utilize both digital and CIM architecture for optimal performance on the various layer characteristics, a low-power SoC, comprising a digital neural network accelerator, an analog CIM core and a RISC-V CPU, is designed to realize simultaneous execution of subsequent layers and high/low precision on corresponding cores<sup>[25]</sup>.

Algorithm-hardware co-design method is utilized for higher energy efficiency. For example, the block-wise weight sparsity and dynamic activation sparsity is proposed to apply sparsity techniques on the regular CIM structure<sup>[14]</sup>. The set-associate block-wise sparsity, tensor-train compression and bitwise sparsity are also explored to save execution time or power consumption<sup>[15, 26]</sup>.

To support high-precision training application, a reconfigurable unified floating point or integer (FP/INT) CIM processor is proposed<sup>[27]</sup>. The activation/weight data are prealigned to the local maximum point so that the CIM macro can execution floating-point MAC operation as the same flow of integral MAC operation.

## 2.2.3. Various devices based CIM chips

SRAM is one of the most popular devices for CIM chip design, while other devices for CIM are also explored, including conventional storage devices such as DRAM or embedded DRAM (eDRAM), and the emerging non-volatile memory (NVM) devices such as resistive RAM (RRAM), spin-transfer torque magneto-resistive RAM (STT-MRAM), phase-change memory (PCM), etc.

DRAM/eDRAM device is adopted for CIM for its high storage density. Xie<sup>[28]</sup> proposes a 16-Kbit eDRAM-based CIM chip, utilizing the intrinsic charge share operation in eDRAM bitcell to implement the DAC/MAC/ADC circuits. A 4-Gb GDDR6-based CIM accelerator is implemented to support various MAC and activation functions<sup>[29]</sup>. The fabricated DRAM die has 16 processing units with corresponding storage banks, and a two 2-KByte global buffer. It supports to activate 16/4 banks simultaneously for different parallelism, with flexible dataflow controlled by the newly defined DRAM command set for deep learning operations. It achieves 1 TFLOPS performance (two die per chip) under BF16 precision.

A three-transistor, one-capacitor (3T1C) dynamic analog RAM (DARAM) structure is proposed<sup>[30]</sup>, which features higher density than SRAM, while achieves higher computing parallelism than DRAM. By storing 4-bit weight in one 3T1C cell, it shows 10× less transistor counts compared with the SRAM-based CIM cell.

RRAM is another well-explored device with macro-level and system-level chip verification. From 2020 to 2022, the foremost storage capacity of RRAM-based CIM macro increases from 2, 4, to 8 Mbit<sup>[31, 32, 19]</sup>. The RRAM-based CIM macros usually adopt current-domain ADCs due to the limited CIM operation voltage<sup>[31]</sup>. The 2's complement weight mapping is explored to reduce the cell usage for multi-bit weight data. To meet the accuracy and energy efficiency requirement, the asymmetric group modulated input and hybrid precision readout circuits are proposed, which separates an 8-bit input data into high 2 bit, middle 3 bit and low 3 bit, and adopts full-precision/reduced-precision for the most/least significant bits<sup>[32]</sup>. The time-based CIM structure is adopted in RRAMbased CIM macro, which shows 5.15× average energy reduction, 1.36× latency reduction, and 1.58× time-step sensing margin<sup>[19]</sup>. The average energy efficiency for 8-bit MAC operation achieves 21.6 TOPS/W. A system-level CIM chip<sup>[33]</sup> is implemented with two fully-connected layers for the MNIST dataset, which shows 78.4 TOPS/W energy efficiency and 94.4% accuracy. The proposed 2T2R array generates the differential current of the positive and negative RRAM cells, which reduces the accumulated source line current, relieve the IR drop, and decreases corresponding ADC power.

Spin-transfer torque magneto-resistive RAM (STT-MRAM)<sup>[34]</sup> and phase-change memory (PCM)<sup>[35]</sup> based CIM macros have also been explored. A 4-Mbit STT-MRAM computing-near-memory macro is fabricated<sup>[34]</sup>, which utilizes a high bit-width of 576 bit organized in bitwise weight-mapping order for near memory partial MAC operation. It also adopts a bidirectional bitline access readout scheme supporting highto-low and low-to-high voltage sensing, which reduces precharge latency and power consumption. A 25.1 TOPS/W energy efficiency is achieved at 50% input sparsity and 8-bit MAC precision. The PCM device is another resistive memory device that can be configured as 1-bit single-level cell (SLC) or multi-level cell (MLC). A PCM macro with 2-M cells is fabricated. It adopts a hybrid SLC-MLC structure, utilizing five SLC/MLC cell for each part of the [7]/[6]/[5:4]/[3:2]/[1:0] bit of a 8-bit weight data. The hybrid SLC-MLC structure shows slight accuracy loss compared with the pure SLC implementation.

Fig. 1 presents the energy efficiency and area efficiency comparison of the CIM macros with different devices. The energy/area efficiency value are scaled to 4-bit input, 4-bit weight. The SRAM-based CIM macros shows better energy efficiency, area efficiency, and higher performance due to several factors. The first influence factor is the more advanced technology node, such as the 5 nm SRAM CIM chip<sup>[20]</sup>. The second factor is that the SRAM-based CIM macros focus on high computation/storage ratio (i.e. higher computation parallelism), which benefits the area efficiency and the performance. On the other hand, the emerging NVM devices and DRAM shows higher storage capacity thanks to the higher storage density. Note that the technology and sparsity influences are not scaled since these features are difficult to scale to an accurate value. The area of RRAM/STT-MRAM/PCMbased macros is estimated from the effective area of the test chip photograph. The area efficiency of DRAM only considers the area of processing units since the total area with storage cells is not reported.

In summary, the CIM chip has become an emerging technology route for more energy-efficient computing and highperformance AI applications, which shows competitive or higher energy efficiency compared with the digital NN processor. The macro/system-level CIM chip keeps moving towards better macro metrics (power, area, performance, accuracy, functionality) and sophisticated CIM architecture with more operator support. CIM on various devices and specific applications is also a promising direction.

## 3. Communication ICs

Telecommunication industry has been growing explosively over the past few decades. Communication ICs, ranging from block-level circuits to system-level transceivers, have attracted intensive attention from both academia and industry. This section covers the latest research trends of communication ICs during the past few years, which includes the following sub-topics: 1) wireless transceivers, 2) wireline and optical communication circuits, 3) phase-locked loops, 4) critical building blocks including power amplifiers, voltage-controlled oscillators, and crystal oscillators.

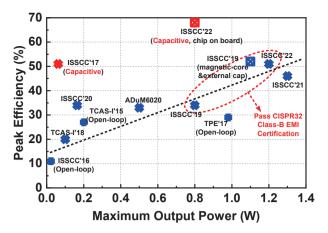

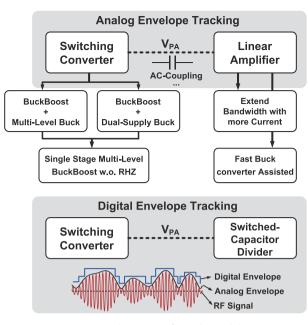

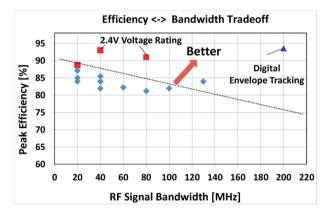

#### 3.1. Wireless transceiver ICs

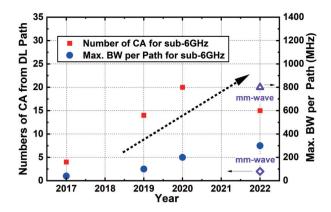

Wireless transceivers are central components of wireless systems. For mobile communication applications, the continuous demand for faster wireless data in the context of mobile battery limitations drives the development of high-throughput and energy-efficient wireless transceivers in more carrier aggregation and wider bandwidth per path, as shown in Fig. 2. Due to growing demand for faster data rate in wireless systems, better resolution requirement in radar system, and emerging sensing applications, mm-wave transceivers for radar and communication have become very attractive in recent years. Ultra-low-power radios are the main building blocks of internet-of-everything connectivity. Bluetooth low-energy (BLE) radios are extensively used for wireless connectivity in many small portable devices, where longer battery life

Fig. 2. (Color online) Trends of the number of CA from downlink path and maximum BW per path for recent cellular SoC implementations.

dramatically improves user experience. In this section, we will discuss, in the following, the state-of-the-arts of high data rate wireless transceivers with multiple mobile communication standards, millimeter-wave and radar transceivers, as well as ultra-low-power radios.

5G radio technology promises tens of Gb/s data-rates with a 10× reduction of latency. This will enable applications in enhanced mobile broadband, massive internet of things and mission-critical services. In Ref. [36], MediaTek introduces a 2/3/4/5G compliant transceiver in 12-nm FinFET CMOS supporting 6-carrier aggregation downlink, 2-carrier aggregation uplink, and  $4 \times 4$  MIMO 256-QAM for the first demonstration of 2 × 2 coherent up-link MIMO. Samsung Electronics demonstrates a highly integrated lost-cost, low-power transceiver IC supporting legacy 2G/3G/4G and new-radio frequency range 1 (FR1) communications with dual-mode global navigation satellite system (GNSS)<sup>[37]</sup>. In this year, Samsung Electronics introduces a digital-IF sub-6GHz FR1 cellular receiver supports up to 15 inter/intra CA by 3 downlink paths with the capability of achieving 300 MHz bandwidth per path in 14-nm FinFET CMOS<sup>[38]</sup>.

Millimeter-wave (mm-wave) wireless communication and radar transceiver systems are the key drivers for cutting-edge integrated circuits design advancement. Mm-wave antenna arrays allow fine beam steering with large radiated power and compact size. Scalability of large-scale arrays to hundreds of elements is necessary to extend the range of mm-wave for 5G and the next-generation radio systems. In Ref. [39], Broadcom presents a 144-element phased-array transceiver using a tiled approach for IEEE 802.11ad. It reports the measured an effective isotropic radiated power (EIRP) of 51 dBm and supports scan angle of  $\pm$  60° in azimuth and  $\pm$  10° in elevation. Samsung demonstrates a 16-channel, 28/39 GHz dual polarized 5G phased-array transceiver IC with a quad-stream IF transceiver supporting non-contiguous carrier aggregation up to 1.6 GHz bandwidth (BW)<sup>[40]</sup>. Transitions from phased-arrays to digital beamforming/MIMO arrays allow increased FDD/TDD/Massive MIMO functionality. Researchers from the University of California Berkeley<sup>[41]</sup> present a 16-element by 16-beam multi-user beamforming integrated receiver with baseband analog BF matrix and on-chip LO generation in 28-nm CMOS technology, which supports up to 2 Gb/s/user wireless links and handles 16 concurrent user streams over the whole band. CMOS radar technologies continue to advance with demonstration of mm-wave MIMO radar, which leads to improved 3D resolution and object discrimination for automotive radar. The work in Ref. [42] demonstrates a 77/79 GHz MIMO radar SoC with 12 transmitters and  $8 \times 2$  receivers resulting in 192 virtual receivers. The radar system based on the IC achieves 6 cm range resolution, 1° angular resolution, and 0.099 km/h Doppler resolution. In addition, two high-level integration 76–81 GHz FMCW MIMO radar module are demonstrated in Refs. [43, 44]. With the continuing advancements of terahertz (THz) technologies in silicon processes, more and more THz transceivers are demonstrated for spectrum-to-space mapping, wideband communication, high resolution mapping<sup>[45, 46]</sup>.

Advances in the ultra-low-power radio continue the drive towards power-efficiency and high sensitivity wireless nodes. In Ref. [47], researchers from Columbia University describe a wake-up receiver achieving a -78.3/-79.1dBm sensitivity at 151.25/434.4 MHz with a 110 ms latency, while consuming 370/420 pW from 0.4 V. It enables practically unlimited battery lifetime for sensor nodes. UWB radio technology promises high data rate and precise positioning over a small distance, which can be useful in many consumer electronic and brain-computer interface applications. Researchers from Yonsei University introduces an IR-UWB radio<sup>[48]</sup> with 1.25 Gb/s data rate over 2 m range while only consuming 28 mW, which is the best among state-of-the-art for energy efficiency at 2 m range up until now.

## 3.2. Wireline and optical communication circuits

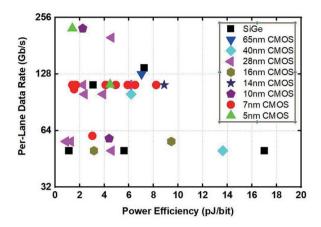

With the development of cloud services and mobile computing, the datacenter drives an ever-growing demand for the high-speed and low power interconnects. In the past three years, the wireline I/Os have witnessed a doubled perchannel data-rate, scaling from 112 to 224 Gb/s. The fourlevel pulse amplitude modulation (PAM-4) has been employed as an enabling technique. To keep the power consumption acceptable, some of the most advanced processes have been utilized, scaling from 7-nm to 5-nm FinFET technology. A universal figure-of-merit factor, pico-Joule-per-bit (pJ/bit), has been widely adopted to evaluate the power efficiency. The trends of wireline communication circuits is briefly summarized in Fig. 3.

Categorized by the communication distance, wireline transceivers employ different wiring channels (copper or fiber) and circuity topologies. In the past three years, the long-reach (LR) and extra short reach (XSR) serializer/deserializer (SerDes), as well as the co-packaged optics (CPO) have attracted the most research attentions worldwide.

## 3.2.1. LR and XSR SerDes

The LR Serdes attempts to overcome up to 40-dB channel loss and beyond 112 Gb/s channel speed. State-of-the-art LR receivers have largely converged on an architecture based on time-interleaved SAR ADCs (RX) and multi-bit equalizer embedded DACs (TX). There are two fundamental design challenges need to be addressed in the SerDes transceivers. Firstly, the data path analog bandwidth keeps increasing, while maintaining about 1-Vpp output swing and sufficient linearity for the PAM-4 signaling. Inverter-based analog frontend circuits are widely adopted to accommodate the advanced CMOS technology<sup>[49–51]</sup>. Hybrid continuous-time linear equalizer (CTLE) architecture with inductive peaking and source degeneration can be used to extend the circuit inher-

Fig. 3. (Color online) Trends of wireline communication circuits: power efficiency and data rate.

ent BW<sup>[52]</sup>. To improve the TX bandwidth, current mode logic (CML) DAC-based output stage with active inductor peaking pushes the data rate to 112 Gb/s PAM-4. High-order Tcoil and  $\pi$ -coil network with precise electromagnetic (EM) modeling can be employed to address the parasitic capacitance from ESD and I/O PADs<sup>[53]</sup>. Secondly, the SerDes transceiver requires high-frequency clock with precise phase spacing and low jitter to serialize and re-time the symbols up to 112 GBaud. Quarter rate serializer architecture has been widely adopted<sup>[49, 54, 55]</sup>, in which the pulse-based MUX and quadrature clock phase calibration are of great importance<sup>[53]</sup>.

High-performance XSR SerDes with both high area efficiency (mm<sup>2</sup>/lane) and energy efficiency (pJ/b) are driven by the interconnects in datacenter, XPU and AI applications. It enables chiplets, multi-die integration for low cost, high yield, and high throughput. The XSR SerDes employs simplified TX DAC and RX DSP functions to save power and area. In Ref. [56], 5-tap TX FIR equalization and a delay-line based continuous-time RX linear equalizer are adopted, realizing 50% power saving and 12% speed improving. Baud-rate PAM-4 CDR instead of multi-bit ADC is utilized to recover the 112 Gb/s data over up to 12 dB loss in an XSR channel. The optimized power efficiency achieves less than 1.5 pJ/bit in a 7nm process<sup>[56]</sup>.

## 3.2.2. Optical links and silicon photonics

The datacenter switch throughput has been growing from 12.8 to 25.6 Tb/s. To support inter- and intra-rack interconnects, the optical links are expected to achieve longer reach (<500 m) at higher data rate (>400 Gb/s). Silicon photonics (Si-Ph) solutions are of particular interest to achieve highdensity integrated 100+ Gb/s/ $\lambda$  optical transceivers, which would be deployed in the CPO modules<sup>[57, 58]</sup>. On the TX side, Si-Ph mirroring modulators (MRMs) have the unique feature of high-Q resonant filtering that can be utilized for the onchip wavelength-division multiplexing (WDM) links. To stabilize the resonance wavelength, a hybrid electrical-optical control loop is necessary to be integrated, while an automatic tuning algorithm is also preferred. In Ref. [57], a 28-nm CMOS driver is co-designed and flipped-chip mounted onto the Si-Ph MRM. The optical TX achieves  $4 \times 112$  Gb/s data-rate and 7.5 pJ/bit power efficiency. The integrated temperature control realizes sub-GHz wavelength tuning resolution at temperatures up to 55 °C. On the RX side, original SiGe transimpedance amplifiers (TIA) are expected to be replaced by CMOS ones for higher integration and lower power. To achieve a comparable sensitivity, digital intensive feedforward equalization (FFE) and decision feedback equalization (DFE) circuits are integrated in the TIA to compensate for the insufficient TIA BW without contributing additional noise<sup>[59]</sup>. Besides of the intensity modulation direct-decision (IMDD) solution, coherent optical transceivers would have longer reach (>2 km) and higher data rate (>640 Gb/s). The first challenge is to design a high-swing and high-linearity modulator driver in CMOS. In Ref. [60], the distributed multi-peaking using on-chip coils and T-lines could significantly extend the analog BW. In addition, the stacked current re-use topology can be adopted to save power in a high-swing driver with sufficient voltage headroom.

In conclusion, after three years of continuous research, the 112 Gb/s/lane wireline circuits have become mature. To save power and further double the speed, more advanced 5-nm CMOS process starts to be adopted as a mainstream technology, enabling the exploring for 224 Gb/s/channel. The full link (TX+RX) power efficiency of 112G LR SerDes has reached 2.2 pJ/bit, while the 224G is still beyond 3 pJ/bit. Optical links would be utilized to replace the copper-wire for meter-scale connectivity and beyond. By co-packaging electronics and silicon photonics, chip-scale high-BW and highdensity throughput would be feasible in the future.

## 3.3. Low-jitter PLL

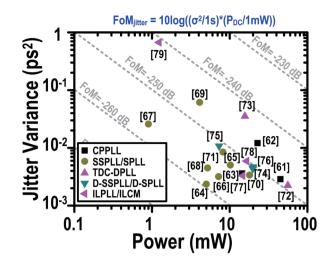

Phase-locked loops (PLL) are widely used in modern ultra-high speed wireless/wireline communication circuits and systems, such as 5G transceivers, over-100-Gbps SerDes transceivers, and high sampling rate analog-to-digital converters (ADCs). Fig. 4 summarizes the recently published representative low-jitter PLLs from recent years' ISSCC or JSSC papers. Based on the recently published works shown in Fig. 4, we will give an overview of the PLL development trends, including the trends of PLL architectures, and the performance gap between integer-N PLL and fractional-N PLL.

Among the PLLs shown in Fig. 4, five PLL architectures are widely used, including charge-pump based PLL (CPPLL)<sup>[61–63]</sup>, sampling/sub-sampling PLL (SPLL/SSPLL)<sup>[64–71]</sup>, time-to-digital converter (TDC) based digital PLL (TDC-based DPLL)<sup>[72, 73]</sup>, and digital sampling/sub-sampling PLL (D-SPLL/D-SSPLL)<sup>[74–76]</sup>, injection-locked PLL (ILPLL)<sup>[77]</sup>, and injection-locked clock multiplier (ILCM)<sup>[78, 79]</sup>.

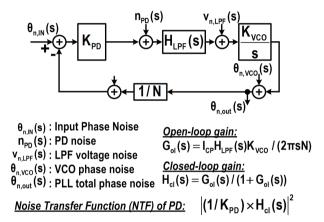

The CPPLL, which adopts a phase/frequency detector (PFD) with unlimited phase and frequency detection range, is simple and robust<sup>[80]</sup>. Thus, it is widely used especially in industry. However, the low PFD gain, which is only  $1/2\pi$ , makes the in-band phase noise of CPPLL (mainly contributed by the CP) difficult to be suppressed<sup>[80]</sup>. Fig. 5 illustrates a simplified linear phase noise model of the PLL with noise transfer function of the PD. It indicates that a low-noise CP with a large CP current is required for the CPPLL to achieve low in-band phase noise and low-jitter performance due to the low gain of PFD. This makes the CPPLL not a suitable choice for low-jitter low-power PLL design. The jitter figure-of-merit FoM<sub>iitter</sub> (the lower the better) of CPPLL, can be improved by newly proposed techniques including the reference frequency multiplier<sup>[62]</sup> and time-amplifying phase detector (PD)<sup>[63]</sup>. However, the FoM<sub>jitter</sub> improvement of the CPPLL is still less than that of the other PLL architectures.

Fig. 4. (Color online) The jitter variance versus power of the recently published PLLs from ISSCC/JSSC.

Fig. 5. Simplified PLL linear phase noise model with its noise transfer function of the PD.

As discussed before, it is significant to increase the PD gain so as to suppress the in-band phase noise to achieve low-jitter with low power consumption. The SSPLLs<sup>[64–69]</sup> adopt a sub-sampling PD (SSPD) to sample the voltage-controlled oscillator (VCO) output signal for phase detection purpose, and thus can achieve high PD gain as the SSPD gain equals the slope of the VCO output signal. Similar to the subsampling PD, the sampling PD (SPD) in SPLL<sup>[70, 71]</sup> achieves similar high PD gain by sampling the sharp edge of the divider output signal for phase detection. In addition, the SPD achieves much higher phase detection range than the SSPD. Thanks to the high PD gain, the SSPLL reported in Ref. [64] achieves the best FoM<sub>iitter</sub> of -259.2 dB with integrated jitter below 50 fs; and several other SSPLLs/SPLLs<sup>[66–68]</sup> obtain FoM<sub>iit-</sub> ter below -255 dB, which are obviously better than that of other PLL architectures.

Digital PLL is getting more popular due to its scalability in advanced CMOS technology and the design portability between technologies. TDC-based PLL<sup>[72, 73]</sup> is a commonly used DPLL architecture. For low-jitter design, a high TDC resolution is required for high PD gain purpose. Recently, Ref. [72] reports the first TDC-based PLL that achieves sub-50-fs integrated jitter with a significantly improved TDC resolution. However, its power consumption of 56 mW is large. Hence, its FoM<sub>jitter</sub> is still higher than –250 dB. This is mainly because that the high resolution TDC with low thermal and flicker noise is usually power hungry.

To relax the power consumption issue, the D-SSPLL/D-SPLLs<sup>[74–76]</sup> are proposed. A low-resolution ADC (including 1bit ADC, which is also called bang-bang PD<sup>[74, 76]</sup>) with low sampling rate of the reference frequency is used to digitalize the output of SSPD or SPD. Hence, it combines the advantages of SSPLL/SPLL's high PD gain and low jitter with DPLL's small area. As illustrated in Fig. 4, D-SSPLL/D-SPLL can achieve FoM<sub>jitter</sub> between –250 and –253 dB. This indicates that the D-SSPLL/D-SPLL can reduce the performance gap.

Besides the PLLs introduced above, the ILCM is also a low-cost solution to achieve low-jitter performance by simply injecting a clean pulse to the oscillator to simultaneously suppress the in-band and output phase noise of the PLL<sup>[70]</sup>. State-of-the-art ILPLLs achieve sub-70-fs integrated jitter and <-250 dB-FoM at the frequency of over-20-GHz<sup>[77, 78]</sup>. The main drawback of the ILPLL or ILCM is its worse spur level compared with other low-jitter PLLs. Hence, low spur level is also a key research focus for ILPLL or ILCM. Recently, the spur level of state-of-the-art ILCM reaches below -70 dBc<sup>[79]</sup>, which is comparable with other low-jitter PLL with low spur level.

As discussed above, the SSPLL/SPLL (including analog and digital architectures) and the ILPLL/ILCM, achieve better performance than the CPPLLs in terms of jitter and FoM<sub>iitter</sub>. However, actually, the CPPLL is still the most widely used architecture in the industry. The main reason is that the unlimited locking range makes the CPPLL robust to maintain its locking state over any disturbance<sup>[80]</sup>; whereas other PLL architectures are more vulnerable to the disturbance because they suffer from the risk of losing lock due to their limited locking range, and thus requires additional settling process for frequency relocking with the help of auxiliary building blocks. However, recently, more and more efforts are made to develop the fast relock technique (e.g. the technique proposed in Ref. [65]) for these PLL architecture to mitigate this issue. This will make these low-jitter PLL architectures more robust and attractive for the industry.

In summary, both analog and digital sampling/subsampling PLLs are popular for low-jitter low-power PLL design, because the analog SSPLL/SPLL achieves the best FoM<sub>jitter</sub> of -259.2 dB and lowest integrated jitter of sub-50 fs, and also dominate the state-of-the-art PLL performance; the digital sampling/sub-sampling PLLs can effectively reduce the performance gap between analog and digital PLLs with the advantage of smaller area. In addition, the development of spur reduction technique makes the ILPLL or ILCM become attractive as a low-cost low-jitter clock generation solution; and the continuous research on the fast relock technique is improving the robustness of the SSPLL/SPLL and ILPLL/ILCM.

#### 3.4. Critical building blocks in communication system

In this subsection, we are going to discuss some commonly used critical building blocks in communication systems, including power amplifiers, voltage-controlled oscillators, and crystal oscillators.

#### 3.4.1. Power amplifiers

Power amplifiers (PAs) are still one of the most important building blocks in wireless transceivers since it dominates the power consumption of transmitters. Therefore, PA is

Fig. 6. (Color online) The state-of-the-art PA peak PAE and  $P_{sat}$  performance in different processes<sup>[90]</sup>.

currently a very active research area. Various PAs spanning from RF bands to terahertz bands towards higher efficiency, higher output power, more compact chip area, and so on are published in recent year's ISSCC and JSSC, including millimeter-wave (mm-wave) CMOS PAs with Watts-level output power, both digital and analog PAs with back-off efficiency enhancement, large-scale power-combining CMOS PA, wideband PAs, and mm-wave PA in GaN HEMT process and in CMOS FinFET process. Fig. 6 surveys the state-of-the-art PAs in different process. Particularly, the frontier mm-wave CMOS PAs have close to 50% peak power added efficiency (PAE) and near 30 dBm saturated output power (P<sub>sat</sub>). Among those works, the major research efforts have been focused on improving the deep back-off efficiency of the PAs, including linear PAs and digital PAs, to support advanced modulation. The most recently published linear PAs work at the millimeter-wave (mm-wave) frequency range, driven by the rapid development of 5G mm-wave communications, where the huge power consumption is still the bottleneck. On the other hand, most digital PAs work at a frequency below 10 GHz due to the degraded transistor switching performance at a higher frequency range.

For mm-wave linear PAs, the Doherty architecture, been invented in 1936 and hot for several decades, is still the most popular technique to improve the back-off efficiency nowadays. Various Doherty PA implementations on silicon have been demonstrated<sup>[81–84]</sup>. In Ref. [81], a mixed-signal Doherty PA composed of an analog main path and a digital auxiliary path is proposed to create multiple back-off efficiency enhance points with a small power step. However, the digital auxiliary path control is complicated, limiting the modulation symbol rates. The textbook Doherty PA uses a quarter wavelength transmission line as the impedance inverter, which is not suitable for on-chip implementation due to the area and insertion loss of long transmission lines. Various on-chip lumped element networks have been proposed to re-

place the transmission lines for compact chip area and low insertion loss<sup>[82-84]</sup>. At a low mm-wave frequency range, transformers are proven to be one of the optimal choices. A parallel-series 3-way transformer-based Doherty PA in 55-nm bulk CMOS is reported in Ref. [82], achieving 20.4% and 14.2% PAE at 6 and 12-dB back-off at 28 GHz. Marchand balun like coupler has also been used in the Doherty PA for wideband back-off efficiency in Ref. [83]. At frequencies higher than 100 GHz, on-chip transformers face degraded performance due to the small diameter, increased parasitics, and reduced port balance. The slotline-based technique proposed in Ref. [84] provides attractive method to realize the on-chip power combining and Doherty operation above 100 GHz. The slotlinebased Doherty PA reported in Ref. [84] has 22.7 dBm saturated power (P<sub>sat</sub>) and 12.1% PAE at 6-dB back-off at 110 GHz. Besides Doherty PA, the recently emerging load-modulated balanced amplifier (LMBA) can also improve the back-off efficiency by modulating the impedance from the isolation port of a hybrid coupler. As demonstrated in Ref. [85], LMBA has the potential for wideband operation. Regarding higher output power, massive-scale power-combining technique has been demonstrated in Ref. [86]. Using 128-to-1 power-combing architecture, the CMOS PA achieves a 1.6 W output power above 100 GHz, which established a new benchmark for CMOS PA.

For digital PAs, the switched-capacitor PA (SCPA) has been the dominated architecture due to its easy implementation, well matching, and flexibility. Recent researches about the SCPA focus on the back-off efficiency enhancement method such as Doherty power-combining, subharmonic switching, and floated-capacitor techniques. Transformer-based power-combining networks introduces Doherty-like operation into SCPAs<sup>[87–89]</sup>. In Ref. [87], an eight-way power-combining transformer enhances the deep back-off efficiency of a 1.5 GHz SCPA. At 6/12/18-dB back-off, the efficiency is enhanced by 1.77/2.12/1.97 times compared with a class-B PA. In Ref. [88], the back-off efficiency is enhanced by reducing the switching frequency of the SCPA in the power back-off region. In Ref. [89], the transformer-based Doherty power-combining together with the floated-capacitor techniques have been used in a 2.4 GHz Watts-level quadrature PA, the power back-off PAE 6-dB of which is 29.1%.

## 3.4.2. Voltage-controlled oscillators

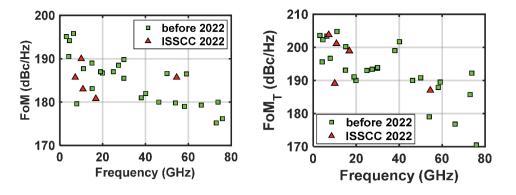

The emerging 5G communication sets a stringent requirement for the phase noise of the local oscillator (LO). As calculated in Ref. [91], the phase noise requirement for 64 QAM at 80 GHz is -102 dBc/Hz at 1 MHz offset frequency. Recently, the effort has been made to improve the phase noise from three directions: the harmonic tuning, the multi-core, and the series-resonant techniques. Fig. 7 summarizes the state-of-the-art oscillator FoM and the FoM with tuning range (FoM<sub>T</sub>) at 1 MHz offset versus frequency.

Harmonic tuning techniques such as class-F, tail filtering, and implicit common-mode resonance have already been proven to be efficient in phase noise improvement, which has been further exploited in recent years<sup>[92, 93]</sup>. In Ref. [92], a single-turn multi-tap inductor is employed in a 25.5-to-29.9 GHz and 191.6 dBc/Hz FoM VCO to create high *Q* high impedance resonances at the 1st, 2nd, and 3rd harmonic frequencies. The single-turn multi-tap inductor has the advantage of higher *Q* in the mm-wave frequency range over conven-

tional multi-turn transformers. In harmonic tuning VCOs, the harmonic peak impedance frequency misalignment degrades the phase noise. In Ref. [93], a head-resonator consisting of two inductors and one capacitor is added to a 5.0-to-6.36 GHz VCO to create a wideband 2nd harmonic response, eliminating the need for dedicated 2nd harmonic capacitor tuning, and suppressing the flicker noise over the whole oscillation frequency range.

It is well known that an N core oscillator can improve the phase noise by 10log(N) times. In Ref. [94], a 3.09-to-4.04 GHz quad-core oscillator using distributed-boosting transformers is proposed. The high-order distributed-boosting transformer network provides the freedom to implement harmonic tuning and impedance expanding in addition to the multicore, which significantly improves the phase noise and FoM. The proposed oscillator achieves excellent -138.9 dBc/Hz phase noise and 195.1 dBc/Hz FoM at 1 MHz offset. The authors in Refs. [95, 96] show that a mode-rejected multi-core topology favors the mm-wave operation compared with resistance-coupled multi-core because the slab topology inductors in the mode-rejected topology can achieve a very small inductor (~20 pH) with considerably high Q (>25). The reported phase noise and FoM of the 60 GHz quad-core<sup>[95]</sup> and 16core<sup>[96]</sup> oscillators are -104.7 and 186.5 dBc/Hz, and -111.1 and 185.7 dBc/Hz at 1 MHz offset, respectively. The multicore oscillator draws more current from the power supply, thus lowering the phase noise. It has an inevitable chip area overhead, although not significant in the millimeter frequency range.

This year, the series resonance VCO presented in Ref. [97] emerges, providing an interesting alternative method that is to draw more current to trade for phase noise. In this work, the LC tank is arranged in a series-connected form, therefore creating a near-short path at the resonance frequency, and drawing a great amount of current from the source using only one single inductor. The VCO reports a phase noise of -138 dBc/Hz and FoM of -190 dBc/Hz at 1 MHz offset from 10 GHz. The series-resonance is a promising low-phase-noise technique with unsettling challenges. The first challenge is the suitable negative resistance in the CMOS process. The second challenge is the frequency tuning range (FTR). To protect the variable capacitance for the boosted voltage swing in the series-resonance VCOs, the efficient max-to-min capacitance ratio is sacrificed through a voltage divider.

Besides low-phase noise, very wide FTR VCOs are also attractive to support the widely distributed frequency bands allocated for 5G communication. Usually one octave FTR is considered sufficient since all lower frequencies can be generated by cascaded frequency dividers, whose design cost is low. The most straightforward way to improve the FTR of an LC oscillator is to scale up the size of the switched-capacitor arrays to improve the max-to-min capacitance ratio. However, this solution faces the fundamental trade-off between the on-resistance and off-capacitance of the transistor switches, which translates to the trade-off between the max-to-min capacitance ratio and the tank Q and the tradeoff between the FTR and phase noise. On the other hand, the mode-switching technique<sup>[98–100]</sup> has shown superior performance on improving the FTR while less affecting the phase noise, which is still a very active research area. In Ref. [98], a dual-mode dual-core VCO using a 4-port resonator exhibits a

Fig. 7. (Color online) The state-of-the-art oscillator FoM and FoM<sub>T</sub> at 1MHz offset versus frequency.

41.3% FTR from 25 to 38 GHz, corresponding to 195 dBc/Hz FoM<sub>T</sub>. To further extend the FTR, a quad-mode quad-core VCO using EM mixed coupling and a triple-mode dual-core VCO using 4-port resonator are proposed in Refs. [99, 100], respectively, which achieve 73.2% FTR from 18.6 to 40.1 GHz with 201.7 dBc/Hz FoM<sub>T</sub> and 80.6% FTR from 7.1 to 16.8 GHz with 204.4 dBc/Hz FoM<sub>T</sub>, respectively.

The mode-switching technique has been proven to be successful in wide FTR VCOs. However, two major design challenges remain. The first is to further reduce the parasitic capacitance introduced by the mode-switching technique, such as the coupling capacitors in Ref. [99] and the off-state crosscoupled pairs in Ref. [100]. The second is to suppress the flicker noise over the more than octave FTR, especially in advanced process nodes, the satisfied solution to which is still missing in literature.

## 3.4.3. Crystal oscillators for IoT devices

Lowering the startup time  $(t_s)$  and energy  $(E_s)$  of the crystal oscillator (XO) for the IoT devices has been an emerging and popular trend in recent years<sup>[101]</sup>. Fueled by the demands on extending the battery lifetime of the IoT devices, or eventually culminating in perpetual operation with energy harvesters, duty-cycling the power-hungry transceivers becomes a popular approach. It effectively reduces the overall power consumption by putting the transceivers into sleep mode for a prolonged period. As an indispensable part of the radio transceiver, the XO is praised for its excellent frequency stability and spectral purity. Yet, these advantages come at the expense of a long  $t_s$  due to the high quality factor (Q) of the quartz crystal; the MHz-range XO takes a matter of milliseconds to start if no startup technique is presented. This long  $t_s$  hampers the duty-cycling operation. Further, the requisite energy to start the XO remains a bottleneck to the power reduction efficacy of the IoT radio brought by the duty-cycling technique.

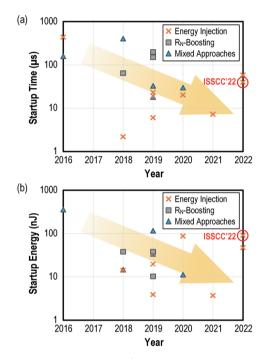

In this regard, there is a thrust to radically improve the  $t_s$  and  $E_s$  of the XO, as shown in Figs. 8(a) and 8(b), such that the IoT transceivers can be duty-cycled efficiently to reduce the average power consumption. Essentially, the fast startup techniques of the XO can be categorized into negative resistance boosting and energy injection. The negative resistance boosting technique boosted the negative resistance  $(R_N)$  of the amplifier sensed by the crystal<sup>[102–111]</sup>. A negative resistance is compulsory to compensate for the resistive loss of the crystal unit and fulfill the Barkhausen stability criterion to support the oscillation of the XO. Besides, the  $R_N$  is also influen-

Fig. 8. (Color online) The trends of (a) startup time and (b) startup energy of the MHz-range fast startup XO.

tial to the  $t_s$ . In the beginning, the XO builds up its amplitude from the thermal noise that existed in the circuit. The growing rate of the XO's amplitude is proportionate to the  $R_N$ . Hence, a high  $R_N$  effectively shortens the  $t_s$  by promoting the exponential growth of the XO's amplitude. As no extra oscillator or sensing circuit is necessary, the hardware overhead for the negative resistance boosting technique is minimized.

Instead of waiting for the crystal to accumulate its amplitude, the quintessence of energy injection technique is to pour energy into the crystal by exciting it with an auxiliary signal<sup>[102, 105, 107, 110–120]</sup>. Although its foundation is relatively straightforward, the injection source must have frequency content in close proximity to the resonant frequency of the crystal ( $\Delta f < 5000$  ppm, depending on the final XO-swing and the injection duration) to excite the crystal effectively due to its high-*Q* bandpass nature. To this end, substantial endeavors have been invested in recent years to properly inject energy to the crystal, such as dithering, two-step injection, signal synchronization, etc. At ISSCC 2022, a fast startup XO based on the energy injection method is proposed<sup>[119]</sup>. The startup of the XO is expedited by the initial dithering and a sampling

Fig. 9. (Color online) Comparison between NS-SAR and conventional architectures.

phase-locked loop (S-PLL). The initial dithering signal generated by the injection voltage-controlled oscillator (i-VCO) is injected into the crystal at the beginning to produce a 0.2-V XO-swing robustly. The frequency of the i-VCO is then locked onto this XO signal by the S-PLL in 8  $\mu$ s. Finally, the accurately locked signal is re-injected to the crystal for another 12  $\mu$ s to yield an XO-swing of 1.2 V. It achieves a  $t_s$  of 39.6  $\mu$ s and  $E_s$  of 92.8 nJ, attaining 18.2× and 6.4× reductions compared to that without startup technique, respectively.

Stimulated by the expansion of the ultra-low-power IoT market, we expect that the research on the fast startup technique for the XO will continue to be active in 2022 and beyond. Even though the  $t_s$  of the fast startup XOs implemented recently are close to the theoretical minimum, for instance, a mere 17% of the  $E_s$  is delivered to the core of the crystal<sup>[118]</sup>. Hence, there is still significant room to improve the energy efficiency of the startup scheme. On top of this, the energy injection technique requires a precise source signal. Consequently, we expect this will also prompt the research on the fully-integrated low-power oscillators<sup>[121, 122]</sup> and associated calibration methods, especially using the signal from the XO itself<sup>[119]</sup>.

## 4. Data converters

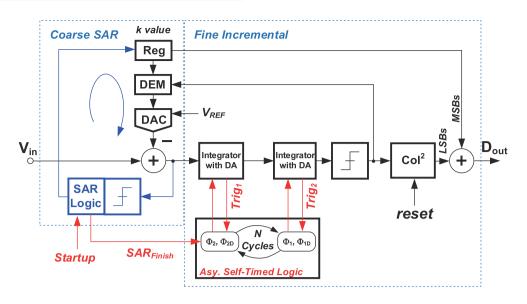

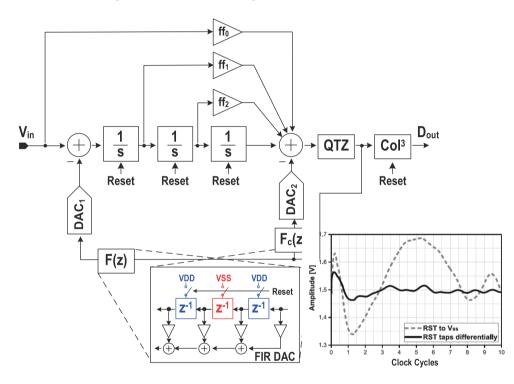

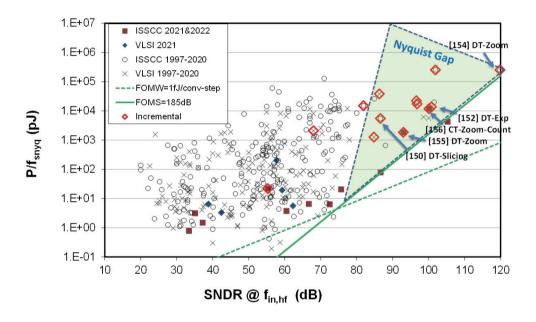

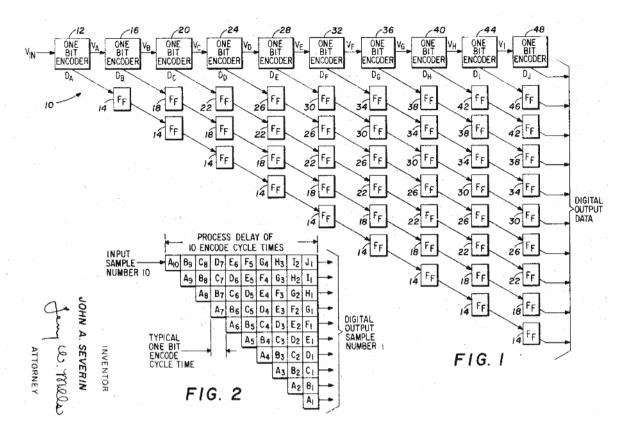

There have been significant advances in the design of data converters over the past decade. This review article covers three major directions as demonstrated in latest ISSCC works. The first one is a novel hybrid architecture called noise-shaping successive approximation register (SAR) ADCs. The second is high-resolution incremental ADC. Last but not

least, state-of-the-art pipelined ADC developments will also be reviewed.

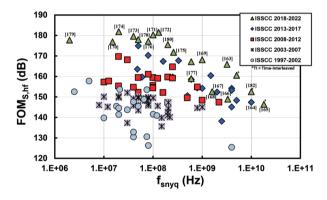

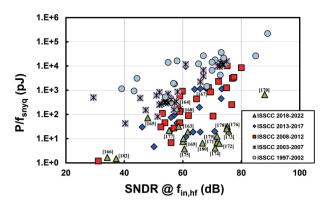

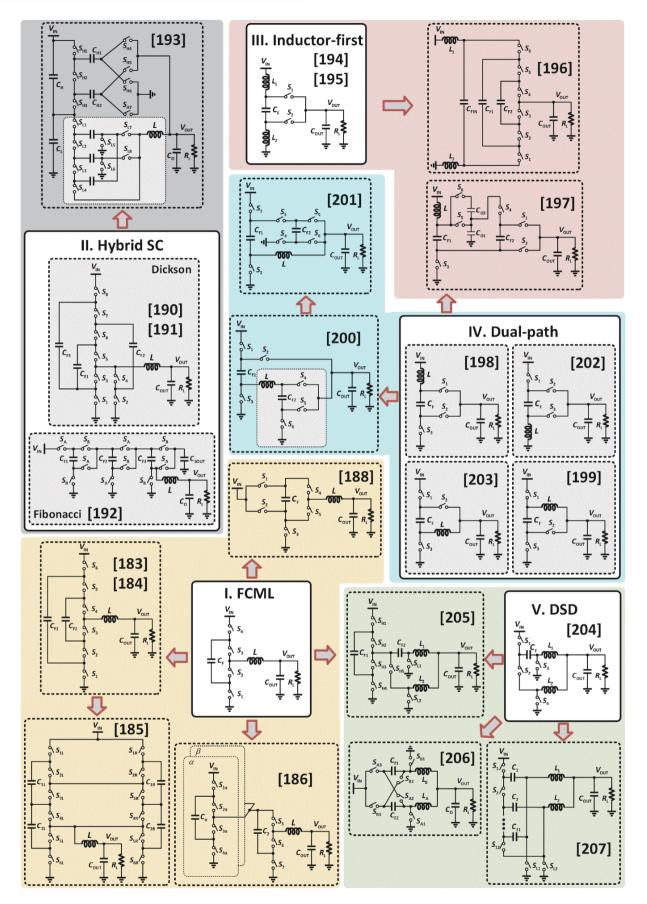

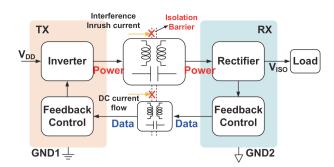

## 4.1. Noise-shaping SAR ADCs

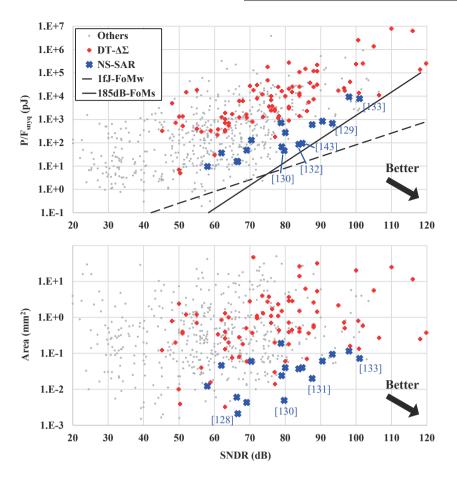

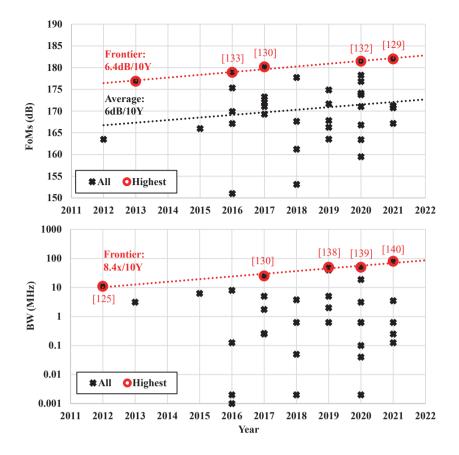

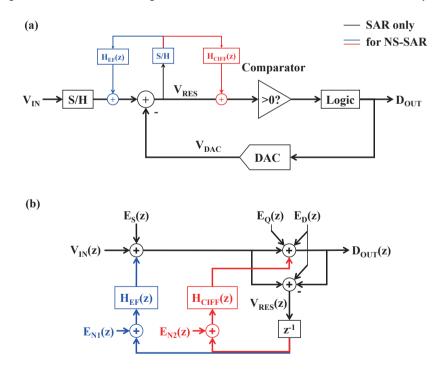

The noise-shaping SAR (NS-SAR) is a promising hybrid architecture emerged in past few years. NS-SAR is a hybridization of the SAR and the delta-sigma (DS) architectures, and it benefits from the both side: it is low-power and area-efficient like SAR, and provides high SNR as DS ADCs. NS-SAR is also easy to down-scale and good for advanced CMOS processes. Fig. 9 shows a power and area comparison between NS-SAR and other architectures<sup>[123]</sup>, where NS-SAR exhibits significant advantages over discrete-time DS ADCs. Therefore, NS-SAR is getting more and more interest from the ADC community recently. Various techniques are proposed and steadily improving the performance of NS-SAR in all aspects. Fig. 10 plots the Schreier figure of merit (FoMs) and bandwidth (BW) of NS-SAR over years. Roughly, FoMs increases by 6.4 dB, and BW increases by 8.4× per decade.

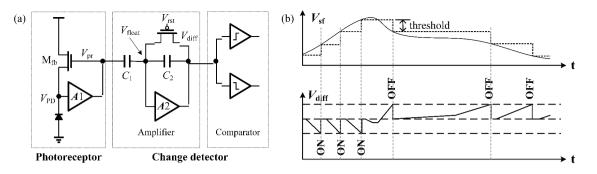

Fig. 11(a) shows a basic framework of NS-SAR, which is modified from SAR ADC<sup>[124]</sup>. Generally, an NS-SAR consists of three parts: 1) A SAR ADC core that samples and quantizes the input signal. In most designs it is a capacitive digital-toanalog converter (CDAC) based one, and a residue voltage ( $V_{\text{RES}}$ ) left on the CDAC at the end of conversion; 2) A loop filter ( $H_{\text{EF}}$  and/or  $H_{\text{CIFF}}$ , depends on architecture) that processes the residue, which is also highly efficient and scalingfriendly; 3) A signal adder that feeds back the loop filter's output. Fig. 11(b) shows the signal model of the NS-SAR in Fig. 11(a), where  $E_{\text{S}}$  is the errors and noise added by samp-