# Low on-resistance 1.2 kV 4H-SiC power MOSFET with $R_{on, sp}$ of 3.4 m $\Omega$ ·cm<sup>2</sup>

# Qiang Liu<sup>+</sup>, Qian Wang, Hao Liu, Chenxi Fei, Shiyan Li, Runhua Huang, and Song Bai

State Key Laboratory of Wide-Bandgap Semiconductor Power Electronic Devices, Nanjing Electronic Devices Institute, Nanjing 210016, China

**Abstract:** A 4H-SiC power MOSFET with specific on-resistance of 3.4 m $\Omega$ -cm<sup>2</sup> and breakdown voltage exceeding 1.5 kV is designed and fabricated. Numerical simulations are carried out to optimize the electric field strength in gate oxide and at the surface of the semiconductor material in the edge termination region. Additional n-type implantation in JFET region is implemented to reduce the specific on-resistance. The typical leakage current is less than 1  $\mu$ A at  $V_{DS} = 1.4$  kV. Drain–source current reaches 50 A at  $V_{DS} = 0.75$  V and  $V_{GS} = 20$  V corresponding to an on-resistance of 15 m $\Omega$ . The typical gate threshold voltage is 2.6 V.

Key words: 4H-SiC; electric field strength; floating guard ring; specific on-resistance

**Citation:** Q Liu, Q Wang, H Liu, C X Fei, S Y Li, R H Huang, and S Bai, Low on-resistance 1.2 kV 4H-SiC power MOSFET with  $R_{on, sp}$  of 3.4 m $\Omega$ -cm<sup>2</sup>[J]. J. Semicond., 2020, 41(6), 062801. http://doi.org/10.1088/1674-4926/41/6/062801

# 1. Introduction

SiC MOSFETs have achieved great improvements, both in device design and material fabrication technology<sup>[1-5]</sup>. Most leading semiconductor companies are working to commercialize SiC MOSFETs. The major designs of SiC MOS-FETs typically follow the 'VDMOS' structure for CREE, ST and 'UMOS' structure for ROHM and Infineon. The former is also called a planar MOSFET and the latter is known as a trench MOSFET. Devices of extremely low on-resistance and medium voltage rating (1200 V / 25 mΩ: C2M0025120D, 900 V / 10 mΩ: CPM3-0900-0010A) are commercially distributed from CREE<sup>[6, 7]</sup>. Meanwhile, devices from ROHM and Infineon both exhibit high gate threshold voltages, making the design of the control system more compatible with that of Si counterparts<sup>[8, 9]</sup>. However, increasing the voltage rating to some extent goes against decreasing on-resistance, and vice versa. Developing devices with both low on-resistance and medium-to-high voltage rating is of great significance and interest. As reported, on-resistance is mainly limited by the low inversion layer mobility ( $\mu_{FE}$ ), which is typically a few tens, much less than the body electron mobility (about 1000 cm<sup>2</sup>·V<sup>-1</sup>·s<sup>-1</sup>)<sup>[2, 10, 11]</sup>. Very high state density ( $D_{it}$ ) at the SiC/SiO<sub>2</sub> interface is thought to heavily restrict the channel mobility<sup>[12]</sup>. Nitric oxide (NO) annealing after oxidation effectively lowered D<sub>it</sub>, thus raising the channelmobility to 20–30 cm<sup>2</sup>·V<sup>-1</sup>·s<sup>-1[13]</sup>. Several methods have been shown that they can increase  $\mu_{\rm FE}$  evidently, such as introducing boron or phosphorus atoms into the gate oxide layer and depositing a thin metallic layer before oxidation<sup>[14–17]</sup>. However, they can only be utilized in industrial manufacture provided long time reliability. Therefore, post-oxidation annealing in NO ambient is still the major adopted process. The process that we employed in manufacturing shows no obvious disadvantage

Correspondence to: Q Liu, liuqiangphy@126.com Received 4 JULY 2019; Revised 20 JANUARY 2020. ©2020 Chinese Institute of Electronics than other manufacturers. Thus, optimizing the epi-layer parameters, cell pitch geometry and doping parameters are regarded as practical methods to enhance the current capability.

In our previous work, we (i.e. Huang) developed a 1200 V / 40 m $\Omega$  MOSFET<sup>[18]</sup>. The resistance of JFET region still limits the total specific on-resistance  $(R_{on, sp})$ . In addition, the area of ohmic contact and gate-to-source gap can be reduced due to the improvement of fabrication recipe. In this paper, we have reduced the on-resistance by additional n-type doping in JFET region, reducing the cell pitch and optimizing the drift layer parameters. According to the simulation results, the electric field strength in JFET region changes with the doping concentration. We have optimized the JFET width to keep the electric field strength under a safe value and we have simultaneously acquired a decreased JFET resistance. Finally, we have achieved a specific on-resistance of about 3.4 mΩ·cm<sup>2</sup>, reduced 47% compared with former work. Consequently, we have designed and fabricated SiC MOSFETs with on-resistance of 15 m $\Omega$  which is a considerable low value in the voltage rating of 1.2 kV.

# 2. Design and simulation

Our simulated models and simulation results will be discussed in this section, including epi-layer parameters, floating guard ring (FGR) type edge termination, cell pitch geometry and JFET region.

#### 2.1. Determination of epi-layer parameters

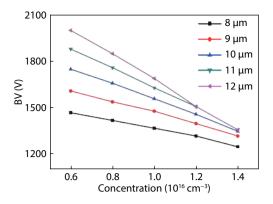

The target voltage rating is mainly supported by the thickness and doping concentration of the epi-layer, which shall be taken into consideration at the beginning of device design. A planar junction with the same doping depth as the P-well is modeled and simulated by SILVACO ATLAS TCAD. Fig. 1 shows the theoretical breakdown voltages (BV) of modeled planar junction structures. The thickness of epi-layer varies from 8 to 12  $\mu$ m, and the n-type doping concentration varies from 6 × 10<sup>15</sup> to 1.4 × 10<sup>16</sup> cm<sup>-3</sup>. The BV increases

Fig. 1. (Color online) Theoretical breakdown voltages of epi-layers with various thickness and doping concentration.

Fig. 2. (Color online) (a) Modeled FGR type edge termination structure. (b) E-field strength profiles comparison between P-well doped and P<sup>+</sup> doped FGR type edge termination. Both data are extracted under breakdown statuses of the two terminations, respectively. Upper one corresponds to E-field at the depth of p-n junction and bottom one corresponds to E-field near the surface of the edge termination.

while adding the thickness and decreasing the doping concentration of epi-layer. Because we aim to design a device with a voltage rating of 1.2 kV, the preferred BV should not be less than 1.5 kV. Following the simulation results, we choose a thickness of 10  $\mu$ m and n-type doping concentration of 1.1 × 10<sup>16</sup> cm<sup>-3</sup> as parameters of the device drift epi-layer, corresponding to a BV of 1510 V. Compared with former results from Huang, the optimization of epi-layer results in specific on-resistance decreasing by about 0.4 mΩ·cm<sup>2</sup>.

# 2.2. Design of float guard ring (FGR) type edge termination

FGR type edge termination is selected thanks to its convenient fabrication process. An FGR with doping profile same with P-well is simulated. Fig. 2(a) shows an edge termination containing 19 rings with 2.5  $\mu$ m width and first ring spacing of 0.8  $\mu$ m. The following spacing between nearby rings in-

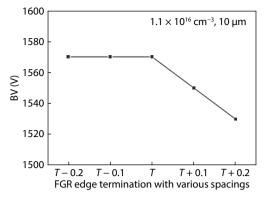

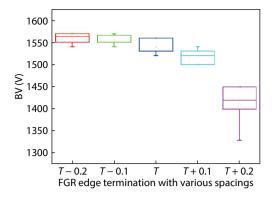

Fig. 3. Breakdown voltages of FGR with different spacing arrays.

creases gradually to 2.4  $\mu$ m. Compared with P<sup>+</sup> doped FGR edge termination, the P-well doped FGR edge termination has a lower maximum electric field (E-field) strength at the depth of p-n junction under breakdown states, as can be seen in Fig. 2(b). P-well and P+ doping was modeled with a junction depth of about 0.8 and 0.6  $\mu$ m, respectively. P-well doping has a retrograde profile and P<sup>+</sup> doping has a boxtype profile with maximal doping concentration over 1  $\times$ 10<sup>20</sup> cm<sup>-3</sup>. The E-field strength near the semiconductor surface is lower for P-well doped termination compared with that of P<sup>+</sup> doped termination, and also under each one's breakdown status. The lower electric field strength near the semiconductor surface indicates a lower drain-source leakage current and a better stability. We furtherly simulate P-well doped FGR edge termination with various ring spacing arrays. The baseline FGR is labeled as 'T', while 'T + 0.1' refers to add 0.1  $\mu$ m to all numbers in array 'T'. 'T + 0.2', 'T - 0.1', and 'T -0.2' are named in the same way. BVs of all FGR edge terminations are presented in Fig. 3. All BVs exceed 1.5 kV and 'T -0.1' is desirable for the sake of stability during manufacture.

#### 2.3. Optimizing the cell pitch

To increase the current density, we constrict the width of P-well implanted region from 9 to 7  $\mu$ m. The specific on-resistance is reduced by about 1.0 m $\Omega$ ·cm<sup>2</sup> while the JFET region is unchanged.

# 2.4. Optimization of electric field strength in gate oxide with additional n-type doping in JFET region

To design a planar type MOSFET, the JFET region is of great concern because of its considerable contribution to the total conducting resistance for MOSFETs with low-to-medium voltage ratings. To reduce the JFET region resistance, additional n-type doping is introduced. Fig. 4(a) shows the specific on-resistance of SiC MOSFET with and without n-type doping in JFET region. Without JFET doping (baseline), the on-resistance increases dramatically when constricting the JFET width. With additional n-type doping, the total doping concentration reaches  $1 \times 10^{17}$  cm<sup>-3</sup> in the JFET region and the specific on-resistance obviously reduces. When choosing the JFET width, the electric field strength near the surface of JFET region is of great concern. When applying a proper  $V_{DS}$  (turn off state) along the surface of JFET region, the electric field strength reaches its maximum at the middle point. The maximum value increases when increasing JFET width. Stronger field in JFET region results in a stronger field in gate oxide. We seek to keep the maximum value of E-field in gate oxide

Fig. 4. (Color online) (a) Specific on-resistance with and without additional JFET doping. (b) Electric field strength in gate oxide and specific on-resistance dependence on JFET width.

Fig. 5. (Color online) Doping regions of designed SiC MOSFET including P-well,  $N^+$ ,  $P^+$ , and JFET regions.

$(E_{max})$  below 4 MV/cm. Consequently, we simulate the electric field strength in gate oxide with JFET doping, the results can be seen in Fig. 4(b). A 2.6  $\mu$ m JFET region is satisfied, at which the specific on-resistance is reduced by about 28% with JFET doping. If  $E_{max}$  is maintained under 3 MV/cm as usual (corresponds to 2.1  $\mu$ m JFET), then the corresponding specific on-resistance will decrease by about 25% with JFET doping. For better reliability of the gate oxide, we choose to use 2.1  $\mu$ m JFET in our design.

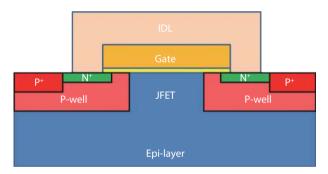

# 3. Fabrication

A 10  $\mu$ m epi-layer with n-type doping concentration of 1.1 × 10<sup>16</sup> cm<sup>-3</sup> was grown on the 'Si face' of a heavily doped n-type 4H-SiC substrate, which was cut with an offset angle of 4 degrees. Doping regions are shown in Fig. 5 including P-well regions, N<sup>+</sup> source regions, P<sup>+</sup> regions, and JFET doping region.

P-well doping with retrograde profile was first achieved by several aluminum implantations. A heavily nitrogen doped

Fig. 6. (Color online) Photo of fabricated 1.2 kV / 15 m $\Omega$  devices.

region with box profile formed N<sup>+</sup> source. The MOS channel was acquired by the self-alignment method, with a length of 0.7  $\mu$ m. P<sup>+</sup> regions were achieved by heavy dose aluminum doping. To reduce the resistance of the JFET region, additional low dose nitrogen doping was implemented. Doping of FGR type edge termination was realized at the same time with P-well process. After all of the doping processes, dopants were activated at 1870 K. Then, gate oxide layer (55 nm) was thermally grown at 1520 K in dry O<sub>2</sub> ambient followed by an annealing process in NO ambient, also at 1520 K. Degenerated doped polysilicon layer (500 nm) was deposited and etched into the gate structure. Ohmic contact between nickel and N<sup>+</sup> source/P<sup>+</sup> region was formed by annealing at 1170 K in vacuum. Intermediate dielectric layer was deposited and via holes were opened soon after. Finally, thick metal layers were evaporated as electrodes at both sides of the wafer. The final wafer is shown in Fig. 6 and the target device is  $5.2 \times 5.5 \text{ mm}^2$  with an active region area of 22.5 mm<sup>2</sup>.

A boron doped polysilicon gate was used instead of a phosphorus doped gate to obtain a higher gate threshold voltage.

# 4. Results and discussion

First, we verify the protection efficiency of FGR type edge termination with P-well doping. The breakdown voltages of PiN diodes are shown in Fig. 7. The designed edge termination structure has a breakdown voltage that is higher than 1550 V.

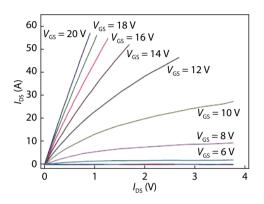

Gate threshold voltage ( $V_{GS}$ ) is measured by applying  $V_{GS} = V_{DS}$  at which  $I_D = 15$  mA, which exhibits a typical value around 2.6 V, increasing by 0.5 V compared with phosphorus doped polysilicon gate. The pulsed current–voltage (I-V) curves under various gate voltages are shown in Fig. 8. This MOSFET conducts 50 A current at  $V_{DS} = 0.75$  V and  $V_{GS} = 20$  V, corresponding to an on-resistance of 15 m $\Omega$  and specific on-resistance of 3.4 m $\Omega$ ·cm<sup>2</sup>.

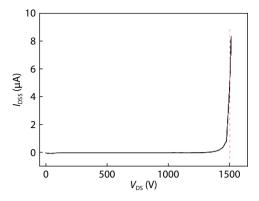

The drain-source leakage current is measured by applying a step-by-step voltage to drain the electrode, while keeping source and gate electrodes shorted to ground. The leakage current is less than 1  $\mu$ A at  $V_{DS} = 1.4$  kV, indicating a good turn off state, as shown in Fig. 9. The dashed-red line rep-

Fig. 7. (Color online) Breakdown voltages of PiN diodes with different FGR spacing arrays.

Fig. 8. (Color online) Current-voltage curves of various gate voltages.

resents  $V_{DS} = 1.5$  kV. The breakdown voltage obviously exceeds 1.5 kV.

#### 5. Conclusion

The design of our device is optimized by including epilayer parameters, cell pitch size, doping concentration in JFET region and width of JFET region. Cell pitch size and JFET region optimizations both make significant efforts to the reduction of specific on-resistance. JFET region needs careful design for both doping concentration and width. These two parameters together count for the on-resistance and E-field in gate oxide (under turn-off state). By reducing cell pitch size, the specific on-resistance decreases by about 1 m $\Omega$ ·cm<sup>2</sup>. By reducing JFET width and adding n-type doping in JFET region, the specific on-resistance decreases by about 1 m $\Omega$ ·cm<sup>2</sup> and the E-field in gate oxide is still in a safe range. Edge termination is also doped by P-well recipe and a lower maximum E-field is achieved under breakdown status. Finally, 1.2 kV / 15 m $\Omega$  SiC MOSFETs are realized with  $R_{on, sp}$  of 3.4 m $\Omega$ ·cm<sup>2</sup>, breakdown voltage exceeding 1.5 kV and gate threshold voltage around 2.6 V.

# Acknowledgements

This work was supported by the National Science and Technology Major Project (No. 2017YFB0102302).

# References

Kimoto T. Material science and device physics in SiC technology for high-voltage power devices. Jpn J Appl Phys, 2015, 54, 4

Fig. 9. (Color online) Drain – source leakage current at  $V_{GS} = 0$  V. The dashed red line represents  $V_{DS} = 1.5$  kV.

- [2] Lichtenwalner D J, Hull B, Pala V, et al. Performance and reliability of SiC power MOSFETs. MRS Adv, 2016, 1, 2

- [3] Castellazzi A, Fayyaz A, Romano G, et al. SiC power MOSFETs performance, robustness and technology maturity. Microelectron Reliab, 2016, 58, 58

- [4] Jiang F, Sheng K, Guo Q, et al. Comparative study of temperaturedependent characteristics for SiC MOSFETs. China International Forum on Solid State Lighting, 2016, 50

- [5] Zhou W, Guo Q, Wu X, et al. A 1200 V/100 A all-SiC power module for boost converter of EV/HEV 's motor driver application. China International Forum on Solid State Lighting, 2016, 38

- [6] https://www.wolfspeed.com/power/products/sic-mosfets/cpm3-0900-0010a

- [7] https://www.wolfspeed.com/power/products/sicmosfets/c2m0025120d

- [8] https://www.rohm.com.cn/products/sic-power-devices/sic-mosfet

- [9] https://www.infineon.com/cms/en/product/power/mosfet/silicon-carbide/discretes/

- [10] Iwata H, Itoh K M. Donor and acceptor concentration dependence of the electron Hall mobility and the Hall scattering factor in n-type 4H- and 6H-SiC. J Appl Phys, 2001, 89, 6228

- [11] Chung G Y, Tin C C, Williams J R, et al. Improved inversion channel mobility for 4H-SiC MOSFETs following high temperature anneals in nitric oxide. IEEE Electron Device Lett, 2001, 22, 176

- [12] Moghadam H A, Dimitrijev S, Han J, et al. Active defects in MOS devices on 4H-SiC: A critical review. Microelectron Reliab, 2016, 60, 60

- [13] Ohashi T, Nakabayashi Y, Shimizu T, et al. Investigation of nitridation and oxidation reactions at SiC/SiO<sub>2</sub> interfaces in NO annealing and modeling of their quantitative impacts on mobility of SiC MOSFETs. Jpn J Appl Phys, 2017, 56, 10

- [14] Fujita E, Sometani M, Hatakeyama T, et al. Insight into enhanced field-effect mobility of 4H-SiC MOSFET with Ba incorporation studied by Hall effect measurements. AIP Adv, 2018, 8, 8

- [15] Fiorenza P, Swanson L K, Vivona M, et al. Characterization of  $SiO_2/SiC$  interfaces annealed in  $N_2O$  or POCl<sub>3</sub>. Materials Science Forum, 2014, 623

- [16] Rong H, Sharma Y K, Mawby P A, et al. Combined N<sub>2</sub>O and phosphorus passivations for the 4H-SiC/SiO<sub>2</sub> interface with oxide grown at 1400 °C. Materials Science Forum, 2016, 344

- [17] Lichtenwalner D J, Pala V, Hull B, et al. High-mobility SiC MOS-FETs with alkaline earth interface passivation. Materials Science Forum, 2016, 671

- [18] Huang R, Liu H, Liu T, et al. Design and fabrication of 1.2 kV/40 m $\Omega$  4H-SiC MOSFET. China International Forum on Solid State Lighting: International Forum on Wide Bandgap Semiconductors China, 2018