文章编号: 1001-9014(2024)01-0085-06

DOI: 10. 11972/j. issn. 1001-9014. 2024. 01. 012

# An improved method for determination of extrinsic resistances for HEMT devices based on 110 GHz S-parameters on-wafer measurement

LI Zhi-Chun<sup>1</sup>, LYU Yuan-Ting<sup>1</sup>, ZHANG Ao<sup>2</sup>, GAO Jian-Jun<sup>1\*</sup>

School of Physics and Electronic Science, East China Normal University, Shanghai 200241, China;

School of Transportation and Civil Engineering, Nantong University, Nantong 226019, China)

**Abstract:** An improved method for determination of extrinsic resistances for 70 nm InP high electron mobility transistor (HEMT) is proposed in this paper. A set of expressions have been derived from the equivalent circuit model under operating bias points ( $V_{gs} > V_{th}$ ,  $V_{ds} = 0$  V). The extrinsic resistances are iterative determined using the discrepancy between simulated and measured S-parameters as an optimization criterion using the semi-analytical method. Good agreement between simulated and measured S-parameters under multi bias over the frequency range up to 110 GHz verifies the effectiveness of this extraction method.

**Key words:** InP high electron mobility transistor (HEMT), equivalent circuit model, extrinsic resistances, modeling

PACS:

## 一种改进的基于110 GHz在片S参数测试的HEMT器件寄生电阻提取方法

李织纯1, 吕渊婷1, 张 傲2, 高建军1\*

- (1. 华东师范大学 物理与电子科学学院,上海 200241;

- 2. 南通大学交通与土木工程学院,江苏南通 226019)

摘要:提出了一种改进的高电子迁移率晶体管寄生电阻提取方法,该方法利用了特殊偏置点  $(V_{ss}>V_{th},V_{ds}=0$  V)的等效电路模型,推导了寄生电阻的表达式,采用半分析法对寄生电阻进行了优化。 $1\sim110~GHz~S$ 参数实测结果和仿真的S参数一致,证明该方法是有效的。

关键词: 铟化磷高电子迁移率晶体管;等效电路模型;寄生电阻;器件建模

## Introduction

Accurate extrinsic resistances extraction for modeling InP HEMT devices is a crucial step in the design and production of high-yield, low-cost millimeter wave circuits<sup>[1]</sup>. The common used methods mainly include numerical optimization method, cold FET method and cutoff method. In optimization method, the extrinsic resistances extraction result strongly depends on the initial value and suffers from non-uniqueness and non-physical meaning<sup>[2]</sup>. In cold FET method, the large gate currents caused by forward-biased run through the gate Schottky junction, which leads to degradation of the gate<sup>[3-6]</sup>. To avoid degradation of device characteristics, some authors proposed cutoff method to extract extrinsic resistances. However, this method is valid only at high frequency (> 18GHz), and the extracted resistances fluctuate widely

over the whole frequency range of interest<sup>[7-9]</sup>.

In order to overcome these limitations, an improved method for determination of extrinsic resistances is proposed. In contrast with previous publications, this extraction method offers the following advantages.

- 1) Under operating bias point ( $V_{gs} > V_{th}$ ,  $V_{ds} = 0$  V), the effect of channel between source and drain can be modeled by resistance  $R_{ch}$ , while the capacitance will be dominant under cutoff bias condition.

- 2) The semi-analytical method which is a combination of optimization method and analytical direct extraction method has been used to determine the extrinsic resistances.

- 3) This extraction method is verified with *S*-parameters on-wafer measurement up to 110 GHz.

Section II gives the equivalent circuit model under

**Received date:** 2023-03-31, revised date: 2023-11-08

收稿日期:2023-03-31,修回日期:2023-11-08

Foundation items: Supported by the National Natural Science Foundation of China (62201293,62034003)

Biography: LI Zhi-Chun (1999—), female, Zhumadian, Henan, master. Research area involves microwave device modeling. E-mail: lizhichun82@163.

<sup>\*</sup>Corresponding author: E-mail: jjgao@ee. ecnu. edu. cn

operating bias point ( $V_{gs} > V_{th}$ ,  $V_{ds} = 0~V$ ) as well as the derivation of analytical expressions. Section III gives the procedure of intrinsic parameters extraction. The measured and simulated results are presented in Section IV. The conclusion is given in Section V.

#### 1 Extrinsic resistances extraction

#### 1.1 Equivalent circuit model

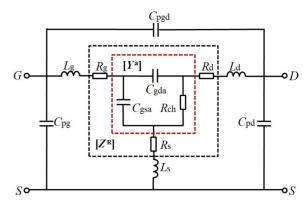

Fig. 1 shows the small-signal equivalent circuit model under operating bias point ( $V_{\rm gs} > V_{\rm th}$ ,  $V_{\rm ds} = 0$  V).  $C_{\rm pgd}$ ,  $C_{\rm pg}$ , and  $C_{\rm pd}$  represent the extrinsic capacitances due to the pad connections.  $L_{\rm g}$ ,  $L_{\rm d}$ , and  $L_{\rm s}$  represent the extrinsic inductances of the gate, drain, and source feedlines.  $R_{\rm s}$  and  $R_{\rm d}$  represent the extrinsic resistances of the source and drain.  $R_{\rm g}$  is the distributed gate resistance.  $C_{\rm gsa}$  and  $C_{\rm gda}$  represent intrinsic gain-source and gain-drain capacitances respectively.  $R_{\rm ch}$  is the channel resistance when the channel between drain and source is open at zero drain bias and gate voltage above threshold voltage.

The intrinsic part of the equivalent circuit model,

Fig. 1 The small-signal equivalent circuit model under operating bias point  $(V_{gs} > V_{th}, V_{ds} = 0 \text{ V})$  图 1 偏置点 (Vgs > Vth, Vds = 0 V)下的小信号等效电路模

which exhibits a PI topology, so it is convenient to describe it by a *Y* matrix as:

Convert  $Y^a$  -parameters to  $Z^a$  -parameters:

$$\begin{split} Z_{11}^{a} &= \frac{Y_{22}^{a}}{Y_{11}^{a} Y_{22}^{a} - Y_{12}^{a} Y_{21}^{a}} = \frac{j\omega C_{\text{gda}} + 1/R_{\text{ch}}}{j\omega (C_{\text{gsa}} + C_{\text{gda}})/R_{\text{ch}} - \omega^{2} C_{\text{gsa}} C_{\text{gda}}} \\ &= \frac{1 + j\omega C_{\text{gda}} R_{\text{ch}}}{j\omega (C_{\text{gsa}} + C_{\text{gda}}) - \omega^{2} C_{\text{gsa}} C_{\text{gda}} R_{\text{ch}}} \end{split} , \quad (2)$$

$$\begin{split} Z_{12}^{a} &= \frac{-Y_{12}^{a}}{Y_{11}^{a}Y_{22}^{a} - Y_{12}^{a}Y_{21}^{a}} = \frac{j\omega C_{\text{gda}}}{j\omega (C_{\text{gsa}} + C_{\text{gda}}) / R_{\text{ch}} - \omega^{2}C_{\text{gsa}}C_{\text{gda}}} \\ &= \frac{j\omega C_{\text{gda}} R_{\text{ch}}}{j\omega (C_{\text{gsa}} + C_{\text{gda}}) - \omega^{2}C_{\text{gsa}}C_{\text{gda}}R_{\text{ch}}} \end{split} , \quad (3)$$

$$Z_{21}^{a} = \frac{-Y_{21}^{a}}{Y_{11}^{a}Y_{22}^{a} - Y_{12}^{a}Y_{21}^{a}} = \frac{j\omega C_{\text{gda}}}{j\omega (C_{\text{gsa}} + C_{\text{gda}})/R_{\text{ch}} - \omega^{2}C_{\text{gsa}}C_{\text{gda}}}$$

$$= \frac{j\omega C_{\text{gda}}R_{\text{ch}}}{j\omega (C_{\text{gsa}} + C_{\text{gda}}) - \omega^{2}C_{\text{gsa}}C_{\text{gda}}R_{\text{ch}}}$$

(4)

$$Z_{22}^{a} = \frac{Y_{11}^{a}}{Y_{11}^{a}Y_{22}^{a} - Y_{12}^{a}Y_{21}^{a}} = \frac{j\omega C_{gsa} + j\omega C_{gda}}{j\omega (C_{gsa} + C_{gda}) / R_{ch} - \omega^{2} C_{gsa} C_{gda}}$$

$$= \frac{j\omega R_{ch} (C_{gsa} + C_{gda})}{j\omega (C_{gsa} + C_{gda}) - \omega^{2} C_{gsa} C_{gda} R_{ch}}$$

, (5)

The Z-parameters of intrinsic part with extrinsic resistances can be expressed as following:

$$Z_{11}^{R} = R_{g} + R_{s} + Z_{11}^{a}$$

, (6)

$$Z_{12}^{R} = R_{s} + Z_{12}^{a}$$

, (7)  $Z_{22}^{R} = R_{d} + R_{s} + Z_{11}^{a}$  , (9)

$$Z_{21}^{R} = R_{\rm s} + Z_{21}^{a} \tag{8}$$

Therefore, we have

$$\operatorname{Re}(Z_{11}^{R} - Z_{12}^{R}) = R_{g} - \frac{\omega^{2} C_{gsa} C_{gda} R_{ch}}{\omega^{4} C_{gsa}^{2} C_{gda}^{2} R_{ch}^{2} + \omega^{2} (C_{gsa} + C_{gda})^{2}}, \quad (10)$$

$$\operatorname{Re}(Z_{12}^{R}) = R_{s} + \frac{\omega^{2} C_{\text{gda}} R_{\text{ch}} (C_{\text{gsa}} + C_{\text{gda}})}{\omega^{4} C_{\text{gsa}}^{2} C_{\text{gda}}^{2} R_{\text{ch}}^{2} + \omega^{2} (C_{\text{gsa}} + C_{\text{gda}})^{2}}, (11)$$

$$\operatorname{Re}(Z_{22}^{R} - Z_{12}^{R}) = R_{d} + \frac{\omega^{2} C_{gsa} R_{ch} (C_{gsa} + C_{gda})}{\omega^{4} C_{gsa}^{2} C_{gda}^{2} R_{ch}^{2} + \omega^{2} (C_{gsa} + C_{gda})^{2}}, \quad (12)$$

By neglecting the high order term  $\omega^4 C_{\rm gs}^{\ \ 2} C_{\rm gd}^{\ \ 2} R_{\rm ch}^{\ \ 2}$ , the extrinsic resistances can be obtained by analytical expressions from real part of  $Z^R$ -parameters:

$$R_{\rm g} = \text{Re}(Z_{11}^{\rm R} - Z_{12}^{\rm R}) - \alpha R_{\rm ch}$$

(13)

$$R_{\rm s} = \text{Re}(Z_{12}^{\rm R}) - \beta R_{\rm ch}$$

(14)

$$R_{\rm d} = \text{Re}(Z_{22}^{\rm R} - Z_{12}^{\rm R}) - (1 - \beta)R_{\rm ch}$$

(15)

where

$$\alpha = -\frac{C_{\rm gs}C_{\rm gd}}{(C_{\rm gs} + C_{\rm gd})^2} , \quad (16)$$

$$\beta = \frac{C_{\rm gd}}{C_{\rm gs} + C_{\rm gd}} \tag{17}$$

$C_{\mbox{\tiny gsa}}$  and  $C_{\mbox{\tiny gda}}$  can be determined at low frequencies :

$$C_{\text{gsa}} = \frac{\text{Im}(Y_{11}^a + Y_{12}^a)}{\omega} \bigg|_{\omega \to 0}$$

, (18)

$$C_{\text{gda}} = -\frac{\text{Im}(Y_{12}^a)}{\omega}\bigg|_{\omega \to 0} , \quad (19)$$

### 1. 2 Extrinsic parameters extraction

The pad capacitances can be determined by measuring an open test structure:

$$C_{\rm pg} = \frac{1}{\omega} \text{Im}(Y_{11} + Y_{12})$$

, (20)

$$C_{\rm pd} = \frac{1}{\omega} \operatorname{Im}(Y_{22} + Y_{12})$$

, (21)

$$C_{\text{pgd}} = -\frac{1}{\omega} \text{Im}(Y_{12}) = -\frac{1}{\omega} \text{Im}(Y_{21})$$

, (22)

The extrinsic inductances  $L_{\rm g}$ ,  $L_{\rm d}$ , and  $L_{\rm s}$  can be determined from the imaginary part of Z-parameters (transformed from measured S-parameters) of the short test structure directly:

$$L_g = \frac{1}{\omega} \text{Im}(Z_{11} - Z_{12})$$

, (23)

$$L_d = \frac{1}{\omega} \operatorname{Im}(Z_{22} - Z_{21})$$

(24)

$$L_s = \frac{1}{\omega} \text{Im}(Z_{12}) = \frac{1}{\omega} \text{Im}(Z_{21})$$

, (25)

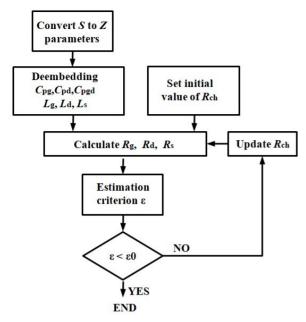

The extraction of extrinsic resistances can be based on the semi-analytical method which is a combination of optimization method and analytical direct extraction method. The extraction procedure is as follows.

- 1) De-embedding the pad capacitances and feedline inductances.

- 2) Set the initial value of the channel resistance  $R_{\rm sh}$ .

- 3) Calculate the extrinsic resistances  $R_{\rm g}$ ,  $R_{\rm d}$ , and  $R_{\rm s}$  using (13)-(15) which can be expressed as functions of  $R_{\rm ch}$  as well as frequency.

- 4) Set error criteria as follows:

$$\varepsilon(R_{\rm ch}) = \sum_{p=1}^{2} \sum_{q=1}^{2} \sum_{i=1}^{N} W_{\rm pq} \left| S_{pq}^{c}(\omega_{i}, R_{\rm ch}) - S_{pq}^{m}(\omega_{i}) \right|^{2}, \quad (26)$$

Where  $S_{pq}^{c}(\omega_{i}, R_{ch})$  represents the calculated S-parameters, and  $S_{pq}^{m}(\omega_{i})$  represents the measured S-parameters.  $\mathcal{E}(R_{ch})$  represents the discrepancy between simulated and measured S-parameters.  $W_{pq}$  are the weighting factors.

5) If error criteria are small enough, the iterative process will be end.

Fig. 2 Flow chart of the algorithm 图 2 算法流程图

## 2 Intrinsic parameters extraction

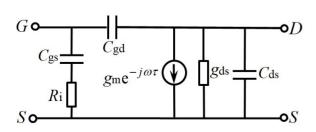

The small-signal circuit model of intrinsic part of InP HEMT devices is illustrated in Fig. 3 after de-embedding the extrinsic parameters, and the intrinsic Y-parameters are described as<sup>[3]</sup>:

$$Y_{11}^{\text{int}} = \frac{R_{i}C_{\text{gs}}^{2}\omega^{2}}{D} + j\omega(\frac{C_{\text{gs}}}{D} + C_{\text{gd}}) , \quad (27)$$

$$Y_{12}^{\text{int}} = -j\omega C_{\text{gd}} , \quad (28)$$

$$Y_{21}^{\text{int}} = \frac{g_{\text{m}}\exp(-j\omega\tau)}{1 + j\omega R_{i}C_{\text{gs}}} - j\omega C_{\text{gd}} , \quad (29)$$

$$Y_{22}^{\text{int}} = g_{\text{ds}} + j\omega(C_{\text{gd}} + C_{\text{gs}}) , \quad (30)$$

with  $D = 1 + \omega^{2}C_{\text{gs}}^{2}R_{i}^{2}$

From the analytical expressions (27)-(30), the intrinsic element values can be obtained directly.

Fig. 3 The small-signal circuit model of intrinsic part 图 3 本征部分的小信号等效电路模型

#### 3 Results and discussion

In this paper, 70 nm InP HEMT devices have been used with 2×30 µm gate width (number of gate fingers× unit gate width). The S-paremeters on-wafer measurement up to 110 GHz using N5247 network analyzer with DC bias by an Agilent B1500A.

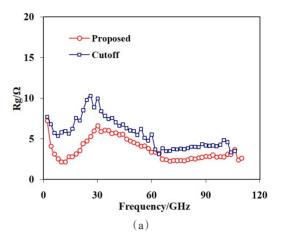

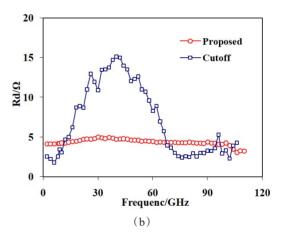

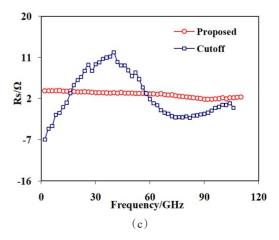

Fig. 4 Extracted extrinsic resistances using the proposed semianalytical method and cutoff method 图 4 半分析方法和截止方法提取的寄生电阻数值对比

Fig. 4 shows the plot of extracted extrinsic resistances versus frequency using the presented semi-analytical method and cutoff method<sup>[9]</sup>. As can be seen from Fig. 4, the extracted  $R_{\rm d}$  and  $R_{\rm s}$  using semi-analytical method are nearly constant versus frequency, while extracted  $R_{\rm d}$  and  $R_{\rm s}$  using cutoff method fluctuate widely versus frequency. These results verify that the proposed extraction method is better than cutoff method <sup>[10]</sup>.

Table 1 gives the values of extrinsic resistances extracted using semi-analytical method. The values of extrinsic capacitances and inductances are given in Table 2. The extracted intrinsic parameters in Section III are shown in Table 3.

| 表 I | 奇生电阻数值              |       |

|-----|---------------------|-------|

|     | Element             | Value |

|     | $R_{ m g}[\Omega]$  | 2. 66 |

|     | $R_{\rm d}[\Omega]$ | 4. 18 |

|     | $R_{ m s}[\Omega]$  | 3.80  |

Table 2 The values of extrinsic capacitance and inductance

表 2 寄生电容和寄生电感数值

| Capacitance           | Values | Inductance           | Values |

|-----------------------|--------|----------------------|--------|

| $C_{pg}[fF]$          | 13. 26 | $L_{\rm g}[{ m pH}]$ | 22. 7  |

| $C_{\rm pd}[{ m fF}]$ | 13. 19 | $L_{\rm d}[{ m pH}]$ | 28. 5  |

| $C_{pgd}[fF]$         | 0. 416 | $L_{\rm s}[{ m pH}]$ | 3. 25  |

Table 3 The values of intrinsic parameters 表 3 本征元件数值

| -pec                           | ν μ    |                       |       |

|--------------------------------|--------|-----------------------|-------|

| Element                        | Value  | Element               | Value |

| $C_{\mathrm{gs}}[\mathrm{fF}]$ | 46. 97 | $g_{\rm m}[{ m mS}]$  | 82. 2 |

| $C_{\mathrm{gd}}[\mathrm{fF}]$ | 9. 69  | $g_{\rm ds}[{ m mS}]$ | 5. 20 |

| $C_{ds}[fF]$                   | 15. 78 | $R_i[\Omega]$         | 3. 46 |

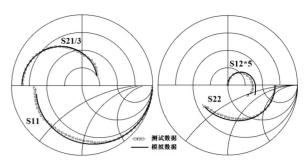

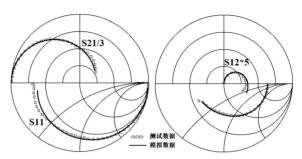

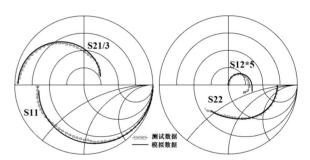

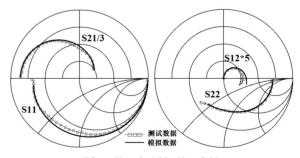

The intrinsic elements listed in Table 2 are substituted into the equivalent circuit model for simulation. Fig. 5 shows the comparison between simulated and measured S-parameters under multi bias. Good agreement between simulated and measured S-parameters are observed in the frequency range of 1 GHz to 110 GHz, which verifies the validity of this developed method to determine the extrinsic resistances.

Table 4 outlines a selection of the accuracy of S-parameters for four different bias points. As can been seen

Bias:  $V_{es} = 0 \text{ V}$ ,  $V_{ds} = 1 \text{ V}$

Bias:  $V_{gs} = 0.1 \text{ V}$ ,  $V_{ds} = 1 \text{ V}$

Bias:  $V_{gs} = 0 \text{ V}$ ,  $V_{ds} = 2 \text{ V}$

Bias:  $V_{gs} = 0.1 \text{ V}$ ,  $V_{ds} = 2 \text{ V}$

Fig. 5 Comparison between simulated (lines) and measured (squares) S-parameters over the frequency range going: from 1 GHz to 110 GHz under multi bias

图 5 1 GHz ~110 GHz 频率范围内多偏置下模拟和测量 S 参数对比曲线

from this table,  $S_{11}$  and  $S_{21}$  maintain an accuracy of around 5%,  $S_{12}$  has an accuracy of less than 5%, and  $S_{22}$

Table 4 Accuracy of S-parameters 表 4 S参数精度

| Bias Condition                                          | $S_{11}$ | $S_{12}$ | $S_{21}$ | $S_{22}$ |

|---------------------------------------------------------|----------|----------|----------|----------|

| $V_{\rm ds} = 1 \mathrm{V} , V_{\rm gs} = 0 \mathrm{V}$ | 5. 45%   | 1. 55%   | 4. 37%   | 2. 59%   |

| $V_{\rm ds} = 1  \rm V$ , $V_{\rm gs} = 0.1  \rm V$     | 5. 46%   | 1. 46%   | 4. 26%   | 2. 45%   |

| $V_{\rm ds} = 2 \mathrm{V} , V_{\rm gs} = 0 \mathrm{V}$ | 4. 99%   | 1. 85%   | 4. 80%   | 2. 74%   |

| $V_{\rm ds} = 2\mathrm{V}, V_{\rm gs} = 0.1\mathrm{V}$  | 5. 82%   | 1. 97%   | 4. 97%   | 4. 04%   |

has an accuracy of between 2%~5%.

#### 4 Conclusion

An approach for determination of extrinsic resistances for 70 nm InP HEMT devices is proposed in this paper. Extrinsic resistances are described as functions of the intrinsic channel resistance, and optimum values can be obtained using semi-analytical method under operating bias point ( $V_{\rm gs} > V_{\rm th}$ ,  $V_{\rm ds} = 0~V$ ). Verification of this extraction method is presented by the good agreement between the simulated and measured S-parameters under multi bias over the frequency range up to 110 GHz.

#### Reference

- [1] Debie P, Martens L. Fast and accurate extraction of parasitic resistances for nonlinear GaAs-MESFET device models [J]. *IEEE Transactions on Electron Devices*, 1995, **42**(12); P.2239-2242.

- [2] Niekerk C V, Meyer P. Performance and limitations of decomposition based parameter-extraction procedures for FET small-signal models [J]. IEEE Transactions on Microwave Theory and Techniques, 1998, 46(11):1620-1627.

- [3] Dambrine, G, Cappy, et al. A new method for determining the FET small-signal equivalent circuit [J]. IEEE Transactions on Microwave Theory and Techniques, 1988.

- [4] Anholt R, Swirhun S. Equivalent-circuit parameter extraction for cold GaAs MESFET's [J]. IEEE Transactions on Microwave Theory and Techniques, 1991, 39(7):1243-1247.

- [5] Yanagawa Ś, Ishihara H, Ohtomo M. Analytical method for determining equivalent circuit parameters of GaAs FETs [J]. IEEE Transactions on Microwave Theory & Techniques, 1996, 44(10):1637-1641.

- [6] Jeon M Y, Kim B G, Jeon Y J. A Technique for Extracting Small-Signal Equivalent-Circuit Elements of HEMTs [J]. IEICE Transactions on Electronics, 1999, 82(11):1968-1976.

- [7] Tayrani, Reza Gerber, Jason E. Daniel, Tom Pengelly, Rayrnond S. Rohde, Ulrich L. A new and reliable direct parasitic extraction method for MESFETs and HEMTs [C]. European Microwave Conference. IEEE, 1993.

- [8] Kim C H, Yoon K S. A new extraction method to determine bias-dependent source series resistance in GaAs FET's [J]. IEEE Transactions on Microwave Theory & Techniques, 1998, 46(9):1242-1250.

- [9] Gao J, Law C L, Wang H, et al. An Improved Pinchoff Equivalent Circuit Model for Determining PHEMT Model Parameters for Millimeterwave Application [J]. International Journal of Infrared & Millimeter Waves, 2002, 23(11):1611-1626.

- [10] Gao J. RF and Microwave Modeling and Measurement Techniques for Field Effect Transistors [M]. IET Digital Library, 2010.