# 320×256 大电荷容量的长波红外读出电路结构设计

翟永成1,2,丁瑞军1

(1. 中国科学院上海技术物理研究所 中国科学院红外成像材料与器件重点实验室, 上海 200083; 2. 中国科学院大学, 北京 100049)

摘 要:长波红外探测器存在暗电流大、背景高的特点,需要设计大电荷容量的读出电路。采用分时 共享积分电容的电路结构,在面阵焦平面的有限单元面积中设计了一种高读出效率、大电荷容量的 320×256长波红外焦平面读出电路。电路输入级采用电容反馈跨阻放大器(CTIA)结构,具有注入效率 高、噪声低、线性度好的特点。基于 CSMC 0.35 μm 标准 CMOS 工艺模型进行了模拟仿真以及版图设 计完成后的后端仿真,电路输出电压范围大于 2 V,非线性小于 1%,帧频为 100 f/s,采用分时共享积分 电容电路结构后,像元有效电荷容量达到 57.5 Me<sup>-</sup>/像元。

关键词:红外焦平面; 读出电路; CTIA; 分时共享; 电荷容量

中图分类号:TN215 文献标志码:A **DOI**: 10.3788/IRLA201645.0904003

## 320×256 LW IRFPA ROIC with large charge capacity

Zhai Yongcheng<sup>1,2</sup>, Ding Ruijun<sup>1</sup>

(1. Key Laboratory of Infrared Imaging Materials and Detectors, Shanghai Institute of Technical Physics, Chinese Academy of Sciences, Shanghai 200083, China; 2. University of Chinese Academy of Sciences, Beijing 100049, China)

**Abstract:** The long-wave infrared detectors present the characteristics of large dark current, high background, large charge capacity readout circuit was need to design. A designing scheme of a high readout efficiency and large charge capacity readout circuit for 320×256 LW infrared focal plane arrays (IRFPAs) in the finite cell area of FPAs was proposed by adopting the circuit structure of time-shared the integrating capacitor. The input stage circuit used the capacitor feedback transimpedance amplifier (CTIA) preamplifier structure, which has a high injection efficiency, low noise and good linearity. The simulation and the simulation after completing the layout were carried out based on CSMC 0.35 μm standard CMOS process model, the output swings of circuit were larger than 2 V and the nonlinearity is less than 1%, the frame rate is 100 f/s, after adopting the circuit structure of the time-shared integrating capacitor, the effective charge capacity reached 57.5 Me<sup>-</sup>/pixel.

Key words: IRFPA; ROIC; CTIA; time-shared; charge capacity

收稿日期:2016-01-10; 修订日期:2016-02-15

基金项目:国家自然科学基金(61505235)

作者简介: 翟永成(1988-), 男, 博士生, 主要从事红外焦平面读出电路设计方面的研究。 Email: zhaiyongcheng@126.com

导师简介:丁瑞军(1964-),男,研究员,博士生导师,主要从事红外器件及集成电路研究、分析和评价等方面的研究。

第 9 期 www.irla.cn 第 45 卷

## 0 引言

近年来,随着红外焦平面研究深入,探测器阵列规模在不断扩大的同时,像元单元面积却存在减小的趋势。读出集成电路(ROIC)是红外焦平面(IRFPA)探测器的重要组成部分,ROIC的性能直接影响IRFPA 探测器的质量。因此,对读出集成电路设计的低功耗、高帧频、大电荷容量等方面的实现提出了更高要求。对于许多成熟的红外焦平面探测器技术来说,读出电路已经是限制其性能的主要部分<sup>[1]</sup>。

在探测器技术上, 焦平面器件规模和焦平面器件的热灵敏度决定了探测器的探测距离和识别能力。选择红外辐射较强的波段,提高读出电路的电荷存储容量是提高探测灵敏度的关键技术<sup>[2-4]</sup>。目前80 K 工作的高性能 HgCdTe 探测器暗电流基本能够达到扩散电流限, 进一步提高探测器性能需要提高读出电路的电荷存储容量<sup>[4]</sup>。

目前的 ROIC 加工工艺一般采用 0.35 µm (3.3 V/5 V)标准 CMOS 工艺,在 30 µm 中心距像元面积内,采用结构简单的直接注入(DI)结构,用 CMOS 电容实现的积分电容约为 2.1 pF,实现的最大积分电荷量约为 36 Me<sup>-</sup>(5 V 电源电压/满阱)<sup>[5]</sup>。文中给出了一种分时共享的长波红外焦平面读出电路结构。在 30 µm中心距像元面积内,电路模拟信号链路采用 CTIA 输入级结构,相比 DI 结构更复杂,可适用于不同的波段。采用 4 个像元单元分时共享一个 CTIA 输入级结构,可以实现大积分电荷容量。在设计过程中,首先进行链路的原理图仿真,其次绘制版图并提取寄生参数,最后进行带寄生参数的后仿真,综合考虑线性度、噪声、功耗、面积和电荷容量等设计指标。

#### 1 整体电路结构设计

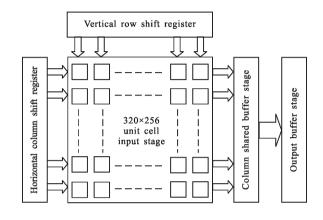

由于长波红外探测器的暗电流和光信号相对于 短波、中波红外探测器大几个数量级,如何有效提高 长波读出电路的电荷容量,像元单元电路面积又成 了一个较大的限制因素。在面阵焦平面的有限单元 面积中设计高读出效率、大电荷容量的电路结构是 长波红外焦平面读出电路的技术难点。文中正是针 对大电荷容量的长波红外读出集成电路的设计展开 研究,设计了一种分时共享的电路结构。 图 1 给出了该读出电路的整体结构框图。该电路包括模拟电路模块和数字电路模块两部分。模拟电路模块是该读出电路的核心,包括像元面阵电路,列共享输出级和视频缓冲输出级 3 部分。模拟电路的性能直接影响读出系统的功耗、频响、线性度等特性。数字电路模块包括列移位寄存器和行移位寄存器。

图 1 整体电路结构框图

Fig.1 Overall circuit structure diagram

在行选择移位寄存器和列选择移位寄存器控制下,读出单元电路输出的电压信号经过多路选择器被逐个串行扫描,顺序传输到阵列外的列共用输出缓冲级,然后经过视频输出级输出。

#### 2 模拟信号链路结构设计与分析

模拟信号链路按照信号传输的顺序依次设计,包括 CTIA 积分模块电路设计,采样保持模块电路设计, 信号传输链路设计以及视频缓冲输出级设计。整个电路的电荷容量、输出摆幅、信噪比等读出指标由模拟信号链路决定,因此它是读出电路设计的关键<sup>[6]</sup>。

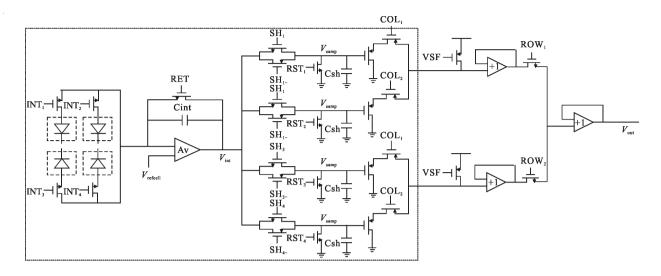

#### 2.1 单元电路结构设计

图 2 是读出电路的模拟信号链路结构示意图。信号先在 CTIA 模块中完成积分,然后采样保持到采样电容上,再传输给后级公共结构。CTIA 积分电容的大小决定了该读出电路的电荷存储能力的大小。大电容需要占用很大的版图面积,在 30 µm 中心距像元面积内很难实现大的积分电容。如图 2 所示,为了提高像元面积利用率,该电路结构采用 4 个像元单元共用一个 CTIA 结构,每个像元单元有一个对应的开关管,开关管的栅压控制信号为积分控制信号 INT1-4,分时选通实现对 CTIA 结构的共用。同

图 2 焦平面读出电路的模拟信号链路

Fig.2 Simulated signal pathway of readout circuit array

时每个像元单元对应一个采样保持电容,当积分完成后信号被采样保持到对应的采样电容上。通过共享方式可在 30 µm 中心距像元面积内实现大的积分电容,使电荷容量提升至 57.5 Me<sup>-</sup>/像元。

图 3 读出电路的工作时序。电路采用先积分后 读出的工作模式,将积分过程和读出过程分开,减少 彼此间的干扰,降低信号噪声。该电路中行/列移位 寄存器都选用由 CMOS 传输门构成的触发器串联而 成。处理模式为单像元处理,采用逐行顺序读出的信 号输出方式。如图 3 所示,在单元 1 顺序读出时间 内, 先 RET 对积分电容进行复位, 复位完成后 INT2 开启单元2选通开关,单元2开始积分,积分完成后 RST2 对采样电容进行复位,复位完成后 SH2 开启采 样开关完成单元2采样并保持,等待后续单元2顺 序读出:在单元2顺序读出时间内,先RET对积分 电容进行复位,复位完成后 INT3 开启单元 3 选通开 关,单元3开始积分,积分完成后RST3对采样电容 进行复位,复位完成后 SH3 开启采样开关完成单元3 采样并保持,等待后续单元3顺序读出;在单元3顺 序读出时间内, 先 RET 对积分电容进行复位, 复位 完成后 INT4 开启单元 4 选通开关,单元 4 开始积 分,积分完成后 RST4 对采样电容进行复位,复位完 成后 SH4 开启采样开关完成单元 4 采样并保持,等 待后续单元4顺序读出:在单元4顺序读出时间内, 先 RET 对积分电容进行复位,复位完成后 INT1 开 启单元1选通开关,单元1开始积分,积分完成后

RST1 对采样电容进行复位,复位完成后 SH1 开启采样开关完成单元 1 采样并保持,等待后续单元 1 顺序读出,实现滚动读出。该电路工作模式让读出时间有效覆盖积分采样时间,同非分时共享积分结构相比并没有额外增加一帧图像积分曝光的时间,实现对时间的有效利用,提高读出效率和帧频。

读出过程中,在奇、偶行选择移位寄存器和奇、 偶列选择移位寄存器控制下,实现奇偶行、奇偶列单 元的交叉顺序读出,即先输出第1行第1列,再输出 第1行第3列,直至输出第1行第255列,第1行奇 数列全部输出结束之后再输出第3行奇数列,直至 输出第319行奇数列,完成单元1的全部读出;接着 输出第1行第2列,再输出第1行第4列,直至输出 第1行第256列,第1行偶数列全部输出结束之后 再输出第3行偶数列,直至输出第319行偶数列,完 成单元2的全部读出:接着输出第2行第1列,再输 出第2行第3列,直至输出第2行第255列,第2行 奇数列全部输出结束之后再输出第4行奇数列,直 至输出第320行奇数列,完成单元3的全部读出;接 着输出第2行第2列,再输出第2行第4列,直至输 出第2行第256列,第2行偶数列全部输出结束之 后再输出第4行偶数列,直至输出第320行偶数列, 完成单元4的全部读出。

Clock 时钟频率设计为4 MHz,单像元信号读出时间为125 ns,采用一路输出,所以320×256 面阵规模一帧图像处理时间为0.010 24 s,帧频可以达到100 f/s。

图 3 焦平面读出电路的工作时序

Fig.3 Timing diagram of readout circuit array

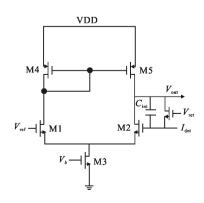

### 2.2 单元 CTIA 结构设计与分析

图 4 是模拟信号链路的单元 CTIA 结构图, $I_{det}$ 为信号光电流, $V_{ref}$ 为放大器偏置电压,因为放大器虚短特性,光电探测器的电压也恒定在该电压上。 $V_{ret}$ 为复位控制信号,实现单元电路的积分与复位。

图 4 单元 CTIA 结构

Fig.4 Structure of CTIA

如图 4 所示,在积分阶段,输出积分电压为:

$$V_{\text{out}} = \frac{A}{A+1} V_{\text{ref}} + \frac{A}{A+1} \frac{I_{\text{det}} \times t}{C_{\text{inf}}}$$

(1)

通过公式(1)的第二项可以看到其注入效率为:

$$\eta = \frac{A}{A+1} \tag{2}$$

因此,通过提高放大器增益,可以提高该读出电路的线性度和注入效率<sup>[7]</sup>。运放增益为:

$$A_{V} = g_{m1}(r_{o1}||r_{o4}) \tag{3}$$

式中: $g_{ml}$  为 M1 管的跨导; $r_{ol}$ , $r_{o4}$  分别为 M1 管、M4 管的输出电阻。

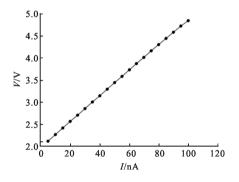

为提高运放增益并降低功耗,优化调节了 M1~M5 管的宽长比,使增益达到 46 dB,工作电流为 1.25 μA。由公式(2)可求得其注入效率为 99.57%。图 5 是该 CTIA 输出级节点积分输出信号电压的线性度仿真结果,积分电压摆幅为 3.2 V,在工作范围内,线性度达到 99.9%。

图 5 CTIA 输出级节点积分信号电压线性度

Fig.5 Linearity of CTIA output integrated signal voltage

CTIA 输入级及单位增益放大器输出缓冲级的输入参考噪声电压为:

$$\overline{V_{n,m}^2} = 5kT\gamma \left( \frac{1}{g_{m1}} + \frac{g_{m4}}{g_{m1}} \right) + \frac{2K_N}{C_{ox}(WL)_{i}f} + \frac{2K_P}{C_{ox}(WL)_{i}f} + \frac{g_{m4}^2}{g_{m1}^2}$$

(4)

式中: $C_{\alpha x}$ 为单位面积栅氧电容; $\gamma$ 为 MOS 管热噪声系数;W、L 分别为 MOS 管的宽和长; $K_N$ 、 $K_P$  分别为 N 管、P 管的闪烁噪声常数。下标 1,4 对应 M1、M4 管  $^{[8]}$  。

传输管噪声为:

$$\overline{V_{n,m}^2} = \frac{kT}{C_{\text{int}}} + \frac{K}{C_{\alpha x}(WL)_{\text{SH}}} \cdot \frac{1}{f} \cdot \frac{g_{m,\text{SH}}^2}{1 + (2\pi f C_{\text{int}} g_{m,\text{SH}})^2}$$

(5)

由上述分析可知: 积分电容  $C_{int}$  的影响最大<sup>[0]</sup>。该设计选用了  $3.4\,\mathrm{pF}$  的积分电容和  $250\,\mathrm{fF}$  的采样电容。

第 9 期 www.irla.cn 第 45 卷

## 3 版图及模拟仿真结果

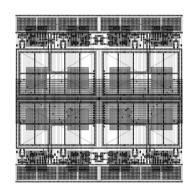

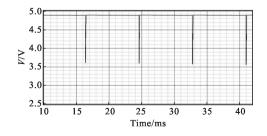

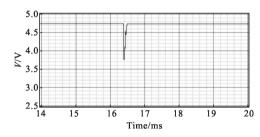

该电路选用了无锡上华的 CSMC 0.35 μm 标准 CMOS 工艺库模型做了原理图模拟仿真以及版图设 计完成后的后端仿真。图 6 为 4×4 单元面阵版图,版 图面积为 120 μm×120 μm。该设计原理图仿真在 Cadence ic51 软件平台下进行,版图的寄生参数使用 Calibre 软件提取。图 7 是在 4 MHz 读出速率下 4×4 单元面阵的前后端仿真结果。如前文所述,由于采用 滚动读出的方式且为单像元信号读出, 所以当所有 单元1读出后才开始读单元2,依次类推,最后在一 路输出中得到连续 4 段单元 1-4 的 1/4 帧图像信 号, 待全部读出后相对应采样到读出电路外的图像 采集系统得到一帧完整图像。仿真时,4x4单元面阵 中 4 个单元 1 的光电流依次设置为 20 nA、40 nA、 60 nA 和 80 nA, 单元 1 的输出结果包含 4 个依次增 强数据信号点,单元2~4也是如此。由仿真结果可以 看出:每1/4帧图像信号中的前4个像元信号"阶 梯"正常,频率响应正常。

图 6 4×4 单元面阵版图 Fig.6 Layout of 4×4 cell array

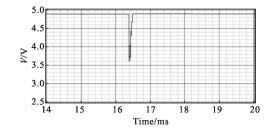

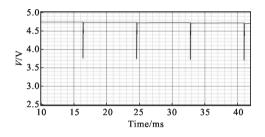

从图 7 前后仿局部放大图的对比中可以看出,随着电路寄生负载的增加,信号建立时间有所增加, 电压输出摆幅有所下降。图 8 为前后仿最终输出电

(a) 4×4 单元面阵前端仿真结果

(a) Front-end simulation of 4×4 cell array

(b) 图 7(a)局部放大

(b) Zoom out result of Fig.7(a)

(c) 4×4 单元面阵后端仿真结果

(c) Back-end simulation of 4×4 cell array

(d) 图 7(c)局部放大

(d) Zoom out result of Fig.7(c)

图 7 4×4 单元面阵前后端仿真结果

Fig.7 Front and back-end simulation of 4×4 cell array

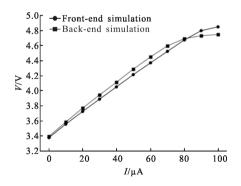

图 8 前后仿输出电压线性度分析图

Fig.8 Output voltage linearity of front-end and back-end simulation

压线性度分析图,从图 8 可以看出:后仿结果较前仿结果线性度有所下降,尤其是在信号电流较大,积分电容接近饱和时,信号线性度下降较多。在有效输出范围内,读出信号线性度良好,经计算其非线性度小

于 0.1%。另外电路的有效线性输出摆幅有所下降, 大约减小了 0.2 V。整体而言,电路各项性能指标与 前仿接近,符合读出电路的设计要求。表 1 给出了读 出电路的主要仿真结果。

#### 表 1 读出电路的仿真结果

Tab.1 Simulation result of readout circuit

| Performance                                          | Results |

|------------------------------------------------------|---------|

| Operating temperature/K                              | 77      |

| Array size                                           | 320×256 |

| Pixel center distance/µm                             | 30×30   |

| Supply voltage/V                                     | 5       |

| Charge capacity/Me <sup>-</sup> •pixel <sup>-1</sup> | 57.5    |

| Frame rate/ $f \cdot s^{-1}$                         | 100     |

| Readout speed/MHz                                    | 4       |

| Power consumption/mW                                 | 159     |

| Nonlinearity                                         | <0.1%   |

| Output swing/V                                       | 1.8     |

### 4 结 论

文中在 30 μm 中心距像元面积内设计了一种大电荷容量的长波红外探测器读出电路结构。为了在有限的单元面积中实现大电荷容量,该电路采用分时共享积分电容的电路结构,单一像元的积分电容达到 3.4 pF,有效电荷容量达到 57.5 Me<sup>-</sup>/像元。在输入级采用了 CTIA 结构,具有注入效率高、噪声低、线性度好的特点。电路整体功能正常,满足长波红外探测器暗电流大、背景高的特点。

### 参考文献:

[1] Liu Liping. Status and trend of the readout circuit technology for IRFPA[J]. *Laser & Infrared*, 2007, 37(7): 598-600. (in

#### Chinese)

- 刘莉萍. 红外焦平面读出电路技术及发展趋势[J]. 激光与红外, 2007, 37(7): 598-600.

- [2] Donald A Reago, Stuart Horn, James Campbell, et al. Third generation imaging sensor system concepts[C]//SPIE, Infrared Imaging Systems: Design, Analysis, Modeling and Testing X, 1999, 3701:108–117.

- [3] Paul Norton, James Campbell, Stuart Horn, et al. Thirdgeneration infrared imagers[C]//SPIE, 2000, 4130: 226-236.

- [4] He Li, Yang Dingjiang, Ni Guoqiang, et al. Introduction to Advanced Focal Plane Arrays[M]. Beijing: National Defense Industry Press, 2011. (in Chinese) 何力, 杨定江, 倪国强, 等. 先进焦平面技术导论 [M]. 北京:国防工业出版社, 2011.

- [5] Bai Piji, Yao Libin. Readout integrated circuit for third-generation infrared focal plane detector [J]. *Infrared Technology*, 2015, 37(2): 89-96. (in Chinese) 白丕绩,姚立斌. 第三代红外焦平面探测器读出电路[J]. 红外技术, 2015, 37(2): 89-96.

- [6] Zhou Jie. 320×256 MW/LW dual-color IRFPAs readout circuits [J]. *Infrared and Laser Engineering*, 2015, 44(10): 2880–2885. (in Chinese) 周杰. 320×256 中/长波双色 IRFPAs 读出电路设计 [J]. 红外与激光工程, 2015, 44(10): 2880–2885.

- [7] Liao Jun. Design of front-end readout circuit for cryogenic infrared focal plane array [D]. Tianjin: Tianjin University, 2012. (in Chinese) 廖峻. 制冷型红外焦平面前端读出电路设计[D]. 天津: 天津大学, 2012.

- [8] Behzad Razavi. Design of Analog CMOS Integrated Circuits[M]. Xi'an: Xi'an Jiaotong University Press, 2002.

- [9] Wang Pan. CTIA input stage design of short-wavelength staring IRFPAs ROIC [J]. *Laser & Infrared*, 2013, 43(12): 1363-1367. (in Chinese) 王攀. 短波 IRFPAs 读出电路 CTIA 输入级的优化设计[J].

激光与红外, 2013, 43(12): 1363-1367.