# 70 nm gate-length InAs PHEMTs with maximum oscillation frequency of 640 GHz

Zhang Lisen, Xing Dong, Xu Peng, Liang Shixiong, Wang Junlong, Wang Yuangang, Yang Dabao, Feng Zhihong

(National Key Laboratory of ASIC, Hebei Semiconductor Research Institute, Shijiazhuang 050051, China)

Abstract: Because of the high electron mobility and two-dimensional electron gas concentration, InP based pseudomorphic high electron mobility transistors (PHEMTs) become one of the most promising three-terminal devices which can operate in terahertz. The InAs composite channel was used to improve the operating frequency of the devices. The two-dimensional electron gas(2DEG) showed a mobility of 13 000 cm<sup>2</sup>/(V · s) at room temperature. 70 nm gate-length InAs/In<sub>0.53</sub>Ga<sub>0.47</sub>As InP-based PHEMTs were successfully fabricated with two fingers 30  $\mu$ m total gate width and source-drain space of 2  $\mu$ m. The T-shaped gate with a stem height of 210 nm was fabricated to minimize parasitic capacitance. The fabricated devices exhibited a maximum drain current density of 1 440 mA/mm ( $V_{GS} = 0.4$  V) and a maximum transconductance of 2 230 mS/mm. The current gain cutoff frequency  $f_T$  and the maximum oscillation frequency  $f_{max}$  were 280 and 640 GHz, respectively. These performances make the device well-suited for millimeter wave or terahertz wave applications.

Key words: InAs-channel; high electron mobility transistor; T shaped gate;

maximum oscillation frequency

CLC Number: TN323<sup>+</sup>.2 Document code: A DOI: 10.3788/IRLA201645.0720004

## 最大振荡频率 640 GHz 的70 nm 栅长 InAs PHEMTs 器件

张立森,邢 东,徐 鹏,梁士雄,王俊龙,王元刚,杨大宝,冯志红

(河北半导体所专用集成电路国家级重点实验室,河北石家庄 050051)

摘 要:由于高的电子迁移率和二维电子气浓度,InP基赝配高电子迁移率晶体管(PHEMTs)器件成为 制作太赫兹器件最有前途的三端器件之一。为提高器件的工作频率,采用 InAs 复合沟道,使得二维电子 气的电子迁移率达到 13 000 cm<sup>2</sup>/(V·s)。成功研制出 70 nm 栅长的 InP 基赝配高电子迁移率晶体管,器 件采用双指,总栅宽为 30 μm,源漏间距为 2 μm。为降低器件的寄生电容,设计 T 型栅的栅根高度达到 210 nm。器件的最大漏端电流为 1440 mA/mm(V<sub>GS</sub>=0.4 V),最大峰值跨导为 2230 mS/mm。截止频率 f<sub>T</sub>和 最大振荡频率 f<sub>max</sub> 分别为 280 GHz 和 640 GHz。这些性能显示该器件适于毫米波和太赫兹波应用。 关键词: InAs 沟道; 高电子迁移率晶体管; T 型栅; 最大振荡频率

收稿日期:2016-02-05; 修订日期:2016-03-07

作者简介:张立森(1985-),男,工程师,博士,主要从事太赫兹固态电子器件方面的研究。Email:zhls1209@163.com

通讯作者:冯志红(1973-),男,研究员,博士生导师,博士,主要从事宽禁带半导体与太赫兹固态电子器件方面的研究。 Email:ga917vv@163.com

#### **0** Introduction

For high resolution imaging and high-frequency wireless communication applications such as medicine, remote atmospheric sensing and radar systems, it is essential to fabricate a low-noise amplifier(LNA) with high gain, large bandwidth, and low power consumption<sup>[1-6]</sup>. InP -based pseudomorphic high electron mobility transistors(PHEMTs) have been proved to be the most promising devices for such demands, because of their high electron mobility, high saturation velocity, and high sheet electron density in the high indium content InGaAs channel <sup>[7]</sup>. The performances of PHEMTs become much better with the increase of indium content. Therefore, the InAs material shows great potential as a channel candidate in high-frequency PHEMTs. Recent reports of record high-frequency characteristics as assessed by the current-gain cutoff frequency  $f_T$  and the maximum oscillation frequency fmax of InAs PHEMTs, have been published. Current records for  $f_T$  and  $f_{\text{max}}$  are 644 GHz using a 30 nm gate-length technology [8] and 1.5 THz using a 25 nm gate-length technology<sup>[9]</sup>, respectively.

In this paper, the design, fabrication, and characteristics of 70 nm gate-length InAs PHEMTs were described. Source and drain ohmic contacts were formed with non-alloyed Ti/Pt/Au. The T-shaped gate with a stem height of 210 nm was fabricated to minimize parasitic capacitance. The frequency characteristics of  $f_{7}$ =280 GHz,  $f_{\text{max}}$ =640 GHz, and  $G_{\text{m,max}}$ =2 230 mS/mm of the device were demonstrated.

### **1** Device fabrication

The epitaxial layers of the PHEMTs were grown on semi-insulating (100) InP substrate by metalorganic chemical vapor deposition (MOCVD). As shown in Fig.1, the layer structure consists of an  $In_{0.52}Al_{0.48}As$ buffer layer, a very thin channel that is composed of  $In_{0.53}Ga_{0.47}As/InAs/In_{0.53}Ga_{0.47}As$ , an  $In_{0.52}Al_{0.48}As$  barrier, an InP etching stop layer, and a bulk-doped In<sub>0.53</sub>Ga<sub>0.47</sub>As cap layer. An Si doping plane was inserted in the Schottky layer to supply electrons for current conduction. The results of hall measurements on this structure with the cap layer removed showed a twodimensional electron gas (2DEG) sheet density of  $3 \times$  $10^{12}$  cm<sup>-2</sup> and a mobility of 13 000 cm<sup>2</sup>/(V · s) at room temperature.

| $n^+$ In <sub>0.53</sub> Ga <sub>0.47</sub> As cap layer             |                   |

|----------------------------------------------------------------------|-------------------|

| InP etching stop layer                                               |                   |

| In <sub>0.52</sub> Al <sub>0.48</sub> As barrier                     | Si doping plane   |

| $In_{\scriptscriptstyle 0.52}Al_{\scriptscriptstyle 0.48}As\ spacer$ |                   |

| In <sub>0.53</sub> Ga <sub>0.47</sub> As                             |                   |

| InAs                                                                 | Composite channel |

| In <sub>0.53</sub> Ga <sub>0.47</sub> As                             |                   |

| $In_{\scriptscriptstyle 0.52}Al_{\scriptscriptstyle 0.48}As$ buffer  |                   |

| InP substrate                                                        |                   |

Fig.1 Schematic of the material structure of InAs PHEMTs

The process of device fabrication was simple. First, the mesa isolation was done by means of a phosphorus acid based wet chemical etching to expose the  $In_{0.52}Al_{0.49}As$  buffer layer. Then, source and drain ohmic contacts were formed with non-alloyed Ti/Pt/ Au with a spacing of 2  $\mu$ m. Transmission line method (TLM) measurements revealed the contact resistance of 0.067  $\Omega$ ·mm on linear TLM patterns, which could be further reduced using improved process.

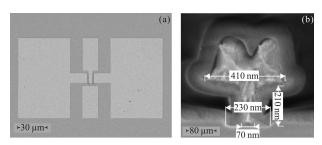

The T-shaped gate process was the most difficult due to its small gate length. A conventional tri-layer resist (ZEP/PMGI/ZEP) was used for EB lithography. After definition of the bottom ZEP layer, the top layers were exposed and developed, which eliminated the effect of gate head exposure energy into the bottom resist layer during gate foot development, so that a much smaller line could be achieved. A two-step recess process was then used to expose the InAlAs barrier. The T-shaped gate with a Ti/Pt/Au metal stack was fabricated with a stem height of 210 nm to minimize parasitic capacitance. Finally, the devices were fully passivated with plasma-enhanced chemical 第7期

vapor deposition  $Si_3N_4$ . SEM images of an InAs PHEMT and 70-nm T-shaped gate were shown in Fig.2.

Fig.2 SEM images of (a) an InAs PHEMT and (b) 70-nm T-shaped gate

#### 2 Results and discussion

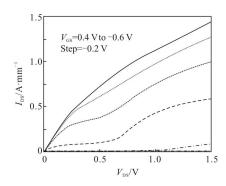

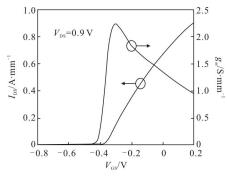

The current-voltage characteristics of fabricated PHEMTs with two fingers 30 µm total gate width measured at room temperature are shown in Fig.3. The gate-source voltage  $(V_{CS})$  is decreased from (top) 0.4 V to (bottom) -0.6 V in steps of -0.2 V. Good pinch-off characteristics were observed at  $V_{GS}$ =-0.6 V. The drain-source current( $I_{DS}$ ) reached about 1440 mA/mm at  $V_{\text{DS}}=1.5$  V and  $V_{\text{GS}}=0.4$  V. The drain current rises with the increase of drain-source voltage ( $V_{DS}$ ) at  $V_{DS}$ > 0.5 V, which is attributed to impact ionization because of the narrow band-gap of InAs channel. Figure 4 shows the  $V_{GS}$  dependence on the  $I_{DS}$  and transconductance  $(G_m)$  of the PHEMTs when biased at  $V_{\rm DS}$  of 0.8 V. The device shows a threshold voltage  $(V_{\text{TH}})$  of about -0.35 V. An maximum transconductance  $(G_{\text{m_max}})$  of 2 230 mS/mm is obtained at  $V_{\text{GS}}$ =-0.24 V, which is attributed to shorter gate-length and higher mobility of InAs channel material.

Fig.3 Output characteristics of the InAs PHEMTs

Fig.4 Transfer characteristics of the InAs PHEMTs

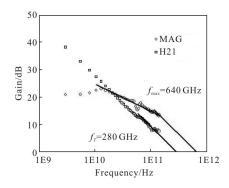

On -wafer small-signal RF performances of devices were characterized with a vector network analyzer, which swept from 1 to 110 GHz and 90 to 140 GHz. S-parameter measurements for open and short pads were also performed on the same wafer in order to calibrate the parasitic capacitance and inductance components related to the pad metals. The current gain H<sub>21</sub> and the maximum stable gain/ maximum available gain(MSG/MAG) of devices were derived from measured S-parameters as a function of frequency. The small signal characteristics of the device with a 70 nm gate length are shown in Fig.5. A cut-off frequency  $f_T$  of 280 GHz was obtained by extrapolating H<sub>21</sub>, and a maximum oscillation frequency  $f_{\text{max}}$  of 640 GHz was achieved by extrapolating MAG/MSG using a least-square fitting with a -20 dB/ decade slope.

Fig.5 Small signal characteristics of the InAs PHEMTs

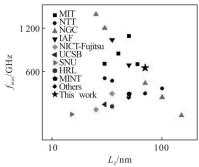

Figure 6 shows  $f_{\text{max}}$  as a function of  $L_g$  for sub-100 nm InGaAs and InAs PHEMTs. When the gatelength is smaller than 50 nm, the short channel effect becomes more severe and the effect of parasitic parameters becomes bigger. So it is difficult to improve the frequency performance by simply reducing the gate-length of the device. Due to the decrease of parasitic capacitance, the obtained  $f_{\text{nax}}$  value in our devices is higher than most of ever reported in PHEMTs above  $L_g = 70$  nm. The excellent frequency performances promise the possibility of THz –wave applications, especially for W –band millimeter-wave devices and circuits. More outstanding device performances would be obtained by optimizing the material structure, reducing the gate length of T–gate and the space of drain-to-source.

Fig.6  $f_{max}$  as a function of  $L_g$  for reported InGaAs and InAs PHEMTs in the literature<sup>[8-27]</sup>

#### 4 Conclusion

In summary, 70 nm gate-length InP-based InAs PHEMTs have been fabricated. A T-shaped gate with a stem height of 210 nm was used to minimize parasitic capacitance. The maximum drain current density and maximum peak transconductance were 1 440mA/mm and 2230mS/mm, respectively. Meanwhile, a current gain cut-off frequency of 280 GHz and a maximum oscillation frequency of 640 GHz were obtained. The excellent performance can be attributed to the high mobility of the InAs material and the short gate-length. Further device fabricated technology can be used to improve device DC and RF performances, such as reducing the source-drain space, gate-length and so on.

#### References:

[1] Axel T. 220-GHz metamorphic HEMT amplifier MMICs for

high-resolution imaging applications [J]. *IEEE Journal of* Solid-State Circuits, 2005, 40(10): 2070–2076.

- [2] Seung J O, Yong M H, Seungjoo H, et al. Medical application of THz imaging technique [C]//37th International Conference on Infrared, Millimeter, and Terahertz Waves, 2012: 1–3.

- [3] Radoslaw P, Thomas K O, Norman K, et al. Short-range ultra-broadband terahertz communications: concepts and perspectives[J]. *IEEE Antennas and Propagation Magazine*, 2007, 49(6): 24–39.

- [4] Ho J S, Tadao N. Present and future of terahertz communications[J]. *IEEE Trans TeraHz Sci Technol*, 2011, 1(1): 256–263.

- [5] Norbert P, Mieczyslaw S, Marcin K, et al. THz spectroscopy and imaging in security applications [C]//19th International Conference on Microwaves, Radar and Wireless Communications, 2012: 265–270.

- [6] Hai B L, Hua Z, Nicholas K, et al. Terahertz spectroscopy and imaging for defense and security applications [J]. *Proceedings of the IEEE*, 2007, 95(8): 1514–1527.

- [7] Lorene A S. An overview of solid-state integrated circuit amplifiers in the submillimeter-wave and THz regime [J].

*IEEE Transactions on Terahertz Science and Technology*, 2011, 1(1): 9–24.

- [8] Dae H K, Jesus A A. 30 nm InAs PHEMTs with  $f_T$  = 644 GHz and  $f_{max}$  =681 GHz [J]. *IEEE Electron Device Letters*, 2010, 31(8): 806–808.

- [9] Xiao B M, Wayne Y, Mike L, et al. First demonstration of amplification at 1 THz using 25 –nm InP high electron mobility transistor process[J]. *IEEE Electron Device Letters*, 2015, 36(4): 327–329.

- [10] Dae H K, Berinder B, Jesus A A.  $f_{\tau}$ =688 GHz and  $f_{max}$ =800 GHz in  $L_g$  = 40 nm In<sub>0.7</sub>Ga<sub>0.3</sub>As MHEMTs with g<sub>m\_max</sub> >2.7 mS/·m [C]//IEEE International Electron Devices Meeting, 2011: 319–322.

- [11] Dae H K, Jesus A A, Peter C, et al. 50 –nm E –mode In<sub>0.7</sub>Ga<sub>0.3</sub>As PHEMTs on 100–mm InP substrate with f<sub>max</sub>> 1 THz [C]//IEEE International Electron Devices Meeting, 2010: 692–695.

- [12] Tae W K, Dae H K, Jesus A A. 60 nm self-aligned-gate InGaAs HEMTs with record high-frequency characteristics [C]//IEEE International Electron Devices Meeting, 2010: 696–699.

- [13] William D, Xiao B M, Kevin M K H L, et al. THz monolithic integrated circuits using InP high electron

mobility transistors [J]. *IEEE Transactions on Terahertz* Science and Technology, 2011, 1(1): 25-32.

- [14] Mike B, Mike B, Xiao B M, et al. Advanced InP and GaAs HEMT MMIC technologies for MMW commercial products

[C]//65th Annual Device Research Conference, 2007: 147 148.

- [15] Leuther A, Axel T, Hermann M, et al. 450 GHz amplifier MMIC in 50 nm metamorphic HEMT technology [C]// International Conference on IPRM, 2012: 229–232.

- [16] Axel T, Leuther A, Hermann M, et al. A high gain 600 GHz amplifier TMIC using 35 nm metamorphic HEMT technology [C]//IEEE CSICS, 2012: 1–4.

- [17] Keisuke S, Wonill Ha, Maik J W R, et al. Extremely high g<sub>m</sub>>2.2 S/mm and f<sub>7</sub>>550 GHz in 30-nm enhancement-mode InP -HEMTs with Pt/Mo/Ti/Pt/Au buried gate [C]//IEEE 19th International Conference on IPRM, 2007: 18–21.

- [18] Wonill Ha, Keisuke S, Griffith Z, et al. High performance InP HEMT technology with multiple interconnect layers for advanced RF and mixed signal circuits [C]//IEEE International Conference on IPRM, 2009: 115–119.

- [19] Akira E, Issei W, Takashi M, et al. High-speed InP HEMTs: low-noise performance and cryogenic operation[C]// 23rd International Conference on IPRM, 2011: 1–4.

- Yoshimi Y, Akira E, Keisuke S, et al. Pseudomorphic In<sub>0.32</sub>Al<sub>0.42</sub>As/In<sub>0.7</sub>Ga<sub>0.3</sub>As HEMTs with an ultrahigh f<sub>T</sub> of 562 GHz[J]. *IEEE Electron Device Letters*, 2002, 23(10): 573– 575.

- [21] Tetsuya S, Haruki Y, Tetsuyoshi I, et al. 30-nm two-step recess gate InP-based InAlAs/InGaAs HEMTs [J]. IEEE Transactions on Electron Devices, 2002, 49(10): 1694–1700.

- [22] Tetsuya S, Haruki Y, Yohtaro U, et al. High-performance 0.1 μm gate enhancement-mode InAlAs/InGaAs HEMT's using two-step recessed gate technology [J]. *IEEE Transactions on Electron Devices*, 1999, 46(6): 1074–1080.

- [23] Seong J Y, Myonghwan P, JeHyuk C, et al. 610 GHz InAlAs/In<sub>0.75</sub>GaAs metamorphic HEMTs with an ultra-short 15 nm gate [C]//IEEE International Electron Devices Meeting, 2007: 613–616.

- [24] Byeong O L, Mun K L, Tae J B, et al. 50 nm T–Gate InAlAs/InGaAs metamorphic HEMTs with low noise and high  $f_{\rm T}$  characteristics [J]. *IEEE Electron Device Letters*, 2007, 28(7): 546–548.

- [25] Sung C K, Dan A, Byeong O L, et al. High performance 94-GHz single balanced mixer using 70-nm MHEMTs and surface micromachined technology[J]. *IEEE Electron Device Letters*, 2006, 27(1): 28-30.

- [26] Elgaid K, McLelland H, Holland M, et al. 50-nm T-gate metamorphic GaAs HEMTs with  $f_T$  of 440 GHz and noise figure of 0.7 dB at 26 GHz [J]. *IEEE Electron Device Letters*, 2005, 26(11): 784–786.

- [27] Kang S Lee, Young S Kim, Yun K Hong, et al. 35 nm zigzag T – gate  $In_{0.52}Al_{0.48}As/In_{0.53}Ga_{0.47}As$  metamorphic GaAs HEMTs with an ultrahigh  $f_{max}$  of 520 GHz[J]. *IEEE Electron Device Letters*, 2007, 28(8): 672–675.