# 高帧频低拖尾帧转移 CCD 驱动技术

陈剑武 1,2,3, 曹开钦 1,2, 孙德新 1,2, 刘银年 1,2

(1. 中国科学院上海技术物理研究所,上海 200083;

2. 中国科学院红外探测与成像技术重点实验室,上海 200083; 3. 中国科学院大学,北京 100049)

摘 要: 帧转移 CCD 在先进高光谱遥感技术中具有非常重要的应用价值, 而拖尾问题是其在高光谱 成像等高帧频应用中存在的最大障碍之一。为了减小拖尾的影响,建立了驱动器、PCB 传输线及 CCD 内部结构一体化的驱动信号传输模型,比传统模型能更准确地预测 CCD 内部和外部的驱动信号波 形:仿真对比了各种典型参数对 CCD 驱动信号波形的影响,仿真与实测结果具有很好的一致性。根据 仿真结果进行了高帧频帧转移 CCD 驱动电路的优化设计,实现了 100 ns 的行转移时间,在 500 fps 的 帧频下获得了拖尾系数小于1%的驱动效果,为进一步提高CCD的工作帧频提供了保障。

关键词: 低拖尾; 高帧频; 帧转移 CCD

中图分类号: TN29 文献标志码·A **DOI**: 10.3788/IRLA201645.0123001

## Driving techniques for high-frame-rate frame transfer CCDs with low smear

Chen Jianwu<sup>1,2,3</sup>, Cao Kaiqin<sup>1,2</sup>, Sun Dexin<sup>1,2</sup>, Liu Yinnian<sup>1,2</sup>

- (1. Shanghai Institute of Technical Physics, Chinese Academy of Sciences, Shanghai 200083, China;

- 2. Key Laboratory of Infrared System Detection and Imaging Technology, Chinese Academy of Sciences, Shanghai 200083, China; 3. University of Chinese Academy of Sciences, Beijing 100049, China)

Abstract: Frame transfer CCDs play a very important role in hyperspectral remote sensing, while smear has become one of the greatest obstacles for frame transfer CCDs used in hyperspectral imaging and other applications with high frame rate. In order to reduce the smear effect, a clock propagation model consisting of the driver, transmission line and the internal structure of the CCD were established, which better predict the clock waveforms inside and outside of the CCD. The effect on the clock waveforms with typical values of the parameters was simulated, and the simulation and measured results shown great consistency. The driving electronics was optimized based on the simulation, resulting in a line transfer time of as short as 100 ns, which is equal to a smear factor of within 1% under a frame rate of 500 fps, showing the ability of frame transfer CCDs to operate at higher frame rates.

Key words: low smear; high frame rate; frame transfer CCD

收稿日期:2015-05-20; 修订日期:2015-06-24

基金项目:国家高技术研究发展计划(2014AA123202)

作者简介: 陈剑武(1987-), 男, 博士生, 主要从事光电成像技术方面的研究。Email:chenjwu2@mail3.sysu.edu.cn

导师简介:刘银年(1971-),男,研究员,博士生导师,博士,主要从事成像光谱技术方面的研究。Email:ynliu@mail.sitp.ac.cn

第1期 www.irla.cn 第 45 卷

### 0 引言

近年来,遥感系统综合性能的提高对光电成像探测器的性能提出了更高的要求。虽然基于有源像素结构的 CMOS 图像传感器技术取得了很大进步,但 CCD 凭借量子效率、电荷容量、读出噪声、均匀性以及空间应用经验等方面的优势<sup>[1]</sup>,仍然是很多遥感仪器的首选探测器。然而,随着成像帧频的提高,拖尾现象已成为 CCD 在高光谱成像等高帧频应用中最大的障碍以及与 CMOS 图像传感器相比最大的劣势之一。

目前针对 CCD 的拖尾问题,解决方法主要有增加机械快门<sup>[2]</sup>、加快帧转移速率以及进行数值校正等。对于帧频高达几十甚至几百帧每秒的应用,不宜使用机械快门,目前研究较多的是拖尾效应的校正方法。然而,现有的校正方法存在诸多局限性,如易受噪声和饱和信号影响<sup>[3]</sup>;对运动图像适应性差,且只适用于具有额外暗像元区域的 CCD<sup>[4]</sup>等。可见虽然拖尾校正方法能在一定程度上改善图像质量,但也无法完全消除图像的失真。而拖尾系数(即帧转移时间与有效积分时间之比)越大,校正后残余的误差也就越大。因此,为了提高遥感应用定量化精度,还需缩短帧转移时间以减小拖尾系数。

要缩短帧转移时间,可以从减少转移行数和缩 短行转移时间两方面着手。减少行数涉及 CCD 面阵 大小的更改,受到成像系统需求的限制;行转移时间 受电荷转移效率的制约,其改进主要依赖于 CCD 设 计和制造工艺以及驱动电路的优化。通用型帧转移 CCD(例如 e2v 公司的 CCD47-20)的行转移时间一 般在1μs以上,帧转移时间在1ms以上,无法满足 高帧频成像对拖尾系数的要求。为了提高转移速率, 目前国外的研究主要集中在 CCD 内部结构的优化 设计方面,如对 CCD 面阵进行分区并对每个分区使 用独立的驱动器以降低对驱动器的要求[5],或使用金 属总线以减小内部分布电阻,并使用差分走线的方 式减小内部分布电感[6]。而国内的研究则主要集中 在电路设计的层面,针对现成的 CCD 进行设计,受 已有 CCD 的性能所限,可达到的行转移速率较低四。 目前已公布参数的帧转移 CCD 中, 行转移时间最快 的是 Sarnoff 公司研制的 CCD160-250-SFT 和 e2v 公司研制的 CCD220,其中前者的行转移时间缩短至250 ns,成功应用于美国的 EMAS-HS 机载高光谱成像仪<sup>[8]</sup>,而后者则实现了低至140 ns 的行转移时间,应用于自适应光学波前检测相机中,该相机号称是当时"最快且灵敏"的相机<sup>[9]</sup>。然而,为了满足遥感系统对信噪比、地面分辨率、幅宽及谱段数的更高需求,需要 CCD 的像元尺寸更大、像元数更多,现成的CCD 难以满足要求;而随着 CCD 面阵尺寸的增大,其内部的分布电容随之成比例增大,会在 CCD 内部引起更严重的驱动时钟衰减,同时也对驱动电路造成更大的挑战。

针对高帧频应用中帧转移 CCD 的拖尾问题,文中采取了 CCD 芯片定制与驱动电路设计紧密结合的方法,进行了 CCD 及驱动电路的建模和仿真,根据仿真结果对驱动电路进行了优化,并对 CCD 芯片设计提出改进要求,取得了显著的效果。

## 1 拖尾现象及其评价方法

拖尾现象是由于在帧转移的过程中感光区继续曝光,使各行像元在其他行的位置进行不需要的积分导致的。由于拖尾对每一列像元的影响规律是一样的,故只需分析其中一列的信号。设 CCD 共有 M 行像元,第 N—1 帧和第 N 帧帧转移时刻信号积分速率分别为 S 和 S'(单位为 DN/s),第 N 帧图像有效信号平均积分速率为 R,有效积分信号为 X(单位为 DN),帧周期为  $T_{\text{FRM}}$ ,有效积分时间为  $T_{\text{INT}}$ ,行转移时间为  $T_{L}$ ,实际读出的信号为 Y,对于第 m 行的像元,有:

$$X = T_{\text{INT}}R \tag{1}$$

$$Y_{m} = T_{\text{INI}} R_{m} + T_{L} \sum_{i=m+1}^{M-1} S_{i} + T_{L} \sum_{i=0}^{m-1} S_{i}^{i}$$

(2)

$$T_{\text{INT}} = T_{\text{FRM}} - (M - 1)T_L \tag{3}$$

公式(2)中:第一项为有效积分数值;第二项为积分前帧转移引起的拖尾数值;第三项为读出前帧转移引起的拖尾数值。可见,拖尾造成的误差与两次帧转移时刻每行信号的大小都有关系。为了更方便地衡量拖尾的影响,令

$$sf = \frac{(M-1)T_L}{T_{\text{FRM}} - (M-1)T_L}$$

(4)

式中:sf表示帧转移时间与有效积分时间的比值,称为拖尾系数。sf越大,表明拖尾越严重。

由公式(2)和公式(4)可见,缩短行转移时间有助

第 1 期 www.irla.cn 第 45 卷

于减小拖尾系数,从而减小拖尾造成的测量误差。然而,行转移时间太短会导致垂直转移效率降低。转移效率可以由扩展像元边缘响应法(EPER)测得,测试时 CCD 焦面施加均匀光照,测得第一行垂直过扫描像元的信号  $X_L$ ,定义残余电荷(Defered charge)系数为  $D_F = X_D/X_L$ ,可以由 $D_F$  求出电荷转移效率。为了直观起见,通常使用  $D_F$  的大小来表征电荷转移效率的好坏。

由上述分析可知,残余电荷系数  $D_F$  制约了行转移时间的缩短,因而 CCD 驱动电路需要在保证  $D_F$  满足要求的前提下减小拖尾系数 sf。

## 2 CCD 驱动电路建模及仿真

#### 2.1 CCD 驱动电路建模

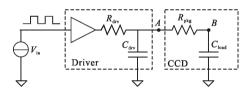

传统的 CCD 驱动电路模型如图 1 所示问,该模型具有简单易用的优点,能满足一般应用的需求。然而,该模型没有考虑驱动时钟信号在 CCD 内部的衰减以及 PCB 的传输线参数,在行转移时间较短时无法准确预测驱动电路的实际表现。为此,需要建立更完整、准确的模型。

图 1 传统 CCD 驱动电路模型

Fig.1 Traditional CCD driving circuit model

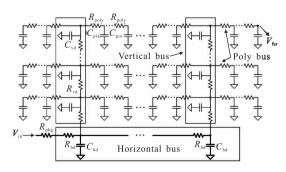

文中所用 CCD 内部结构如图 2 所示。其中, $R_{pkg}$ 为封装电阻, $R_{hd}$ 、 $C_{hd}$  分别为水平金属总线的分布电阻和电容, $R_{vd}$ 、 $C_{vd}$  分别为垂直金属总线的分布电阻和电容, $R_{poly}$  为多晶硅总线分布电阻, $C_{pix}$  为单个相

图 2 文中所用 CCD 内部结构

Fig.2 Internal structure of CCD for this paper

位的像元电容。该模型能准确描述驱动时钟从 CCD 引脚传输到远端像元处的变化,但由于面阵规模庞大,需要仿真超过 50 万个 RC 单元组成的时钟树,就仿真所需的内存空间和运行时间而言,一般个人计算机和常用仿真软件难以实现。为此,需要提出简化的模型。

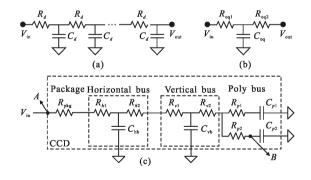

该 CCD 内部可分为水平总线、垂直总线和多晶硅总线三个结构层次,每个层次都可以由图 3(a)的模型表示。其中, $R_d$ 为每两个节点之间的分布电阻, $C_d$ 为每个节点的分布电容。根据 Elmore 延迟的计算方法 $^{[10]}$ ,从  $V_{in}$  到  $V_{out}$  的延迟时间常数为:

$$\tau = \sum_{i=1}^{N} C_d \sum_{j=1}^{i} R_d = \frac{C}{N} \frac{R}{N} \frac{N(N+1)}{2} = RC \frac{N+1}{2N}$$

(5)

式中: $R=NR_d$ 为总的电阻值; $C=NC_d$ 为总的电容值。

求得延迟时间常数后,可以采用一阶 RC 模型 来近似所考虑的网络。为了综合考虑对于前级电路的负载电容、对于后级电路的输出电阻以及本级电路的时间常数,使用 T 型等效 RC 模型,如图 3(b)所示,其中

$$C_{\text{eq}} = C \tag{6}$$

$$R_{\text{eql}} = \frac{\tau}{C_{\text{eq}}} = \frac{R(N+1)}{2N}, R_{\text{eq2}} = R - R_{\text{eq1}} = \frac{R(N-1)}{2N}$$

(7)

使用该等效模型对多晶硅总线及垂直总线分别进行简化,并进行对比仿真,表明该简化模型与原始模型能很好地互换,并比原始模型显著节省了仿真资源和时间,从而使全面阵的仿真成为可能。经简化后,图2所示模型可以使用图3(c)所示模型代替。

图 3 CCD 内部简化模型

Fig.3 Simplified internal structure of the CCD

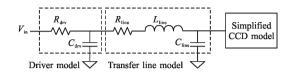

对于成像光谱仪等遥感仪器,由于其特殊的光学和机械结构设计的要求,CCD驱动器往往很难紧靠 CCD 放置。为了评估驱动器与 CCD 之间的 PCB

第 1 期 www.irla.cn 第 45 卷

走线参数对驱动信号的影响,需要建立其传输线模型,从而得到完整的驱动电路模型,如图 4 所示。

图 4 完整的 CCD 驱动电路模型

Fig.4 Complete model of the CCD driving circuit

#### 2.2 CCD 驱动器对驱动时钟波形的影响

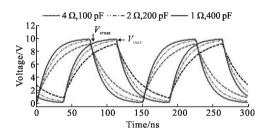

对于高帧频大面阵 CCD,由于驱动器的负载电容大、时钟频率高,对峰值驱动电流的需求往往达到数安培甚至十几安培,驱动芯片的性能参数对驱动效果影响很大,其中的关键参数是导通电阻  $R_{\rm dv}$  及输出电容  $C_{\rm dv}$ 。设行转移时间为 300 ns,相应的驱动时钟周期为 150 ns,仿真得到在几种典型  $R_{\rm dv}$  和  $C_{\rm dv}$ 下,图 3(c)中 B 点(即 CCD 内部离驱动引脚最远处,以下简称 B 点)的信号波形如图 5 所示。从图中可见,随着  $R_{\rm dv}$  的减小,驱动时钟的峰值电压  $V_{\rm max}$  和相邻相位交叉点电压  $V_{\rm cross}$  的衰减都得到改善。另外的计算及仿真表明,由于  $C_{\rm dv}$  相对于 CCD 负载电容较小,故对于时钟波形几乎没有影响。

图 5 不同导通电阻下 B 点的波形 Fig.5 Waveforms at point B with different  $R_{dv}$

#### 2.3 PCB 传输线参数对驱动时钟波形的影响

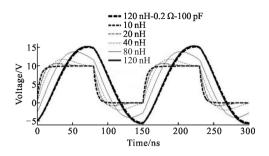

为了衡量 PCB 走线对驱动信号的影响,需要使用不同的传输线参数进行仿真。令  $R_{\rm div}$ =1  $\Omega$ ,  $R_{\rm line}$  和  $C_{\rm line}$  均为 0,则在不同  $L_{\rm line}$  下,图 3(c)中 A 点(即 CCD 引脚处,以下简称 A 点)的仿真波形如图 6 所示。由图可见,随着  $L_{\rm line}$  增大,驱动时钟上升时间加长、过冲增大,信号产生严重畸变。另外,图中还显示了在  $R_{\rm line}$  和  $C_{\rm line}$  和  $C_{\rm line}$  相对于 CCD 内部电阻和负载电容较小,其影响可以忽略,起主要影响的因素是  $L_{\rm line}$  的值。

图 6 不同电感值下 A 点的波形

Fig.6 Waveforms at point A with different inductances

#### 2.4 CCD 内部参数对驱动时钟波形的影响

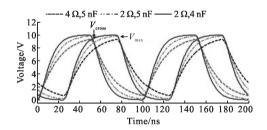

高频驱动时钟在 CCD 内部传输时,会由于内部电容负载的充放电作用而导致边沿减缓乃至幅度衰减。在文中所用 CCD 中,由于水平金属总线上连接的容性负载最大,对驱动时钟的影响也最大。令  $R_{dv}=1\Omega$ , $L_{line}=10\,\mathrm{nH}$ ,在  $100\,\mathrm{ns}$  时钟频率下,对水平总线电阻  $R_{hb}$ (即  $R_{hl}+R_{l2}$ )和电容负载  $C_{hb}$  取不同值,得到 B 点的仿真波形如图  $7\,\mathrm{所示}$ 。由图可见,减小水平总线电阻和电容都能有效减少驱动时钟的衰减,而这也正是主流厂商在高帧频 CCD 设计时考虑的重要因素。

图 7 CCD 优化前后 B 点的波形

Fig. 7 Waveforms at point B before and after CCD optimization

#### 2.5 CCD 驱动电路的优化设计

由以上仿真结果可知,驱动器的导通电阻、CCD的水平总线电阻和电容都会引起时钟信号边沿减缓、幅度衰减,给转移效率和满阱电子数造成损失;而PCB传输线的回路电感则容易与负载电容产生谐振,造成过冲,这将会导致相应相位下的峰值电势点过于靠近二氧化硅界面,当信号电子数较多时,部分电子受界面态捕获,引起转移效率恶化,因而满阱电子数降低 $^{\text{III}}$ 。可见,信号衰减或过冲太大均可能导致满阱容量下降。由 CCD 厂商提供的资料可知,文中所用的 CCD 最佳工作状态需满足  $V_{\text{max}}$ =10 V±0.5 V,对  $V_{\text{cross}}$ 则无明确要求,但其上限也不应超过10 V+0.5 V,下限则越接近  $V_{\text{max}}$  越好。为此,文中对

PCB 进行了优化,并对 CCD 芯片设计提出改进要求。令 PCB1 代表优化前的状态,其关键参数为  $R_{line}$ =  $0.09\,\Omega$ ,  $L_{line}$ =  $100\,\mathrm{nH}$ ,  $C_{line}$ =  $100\,\mathrm{pF}$ ; PCB2 为优化后的状态, $R_{line}$ =  $0.12\,\Omega$ ,  $L_{line}$ =  $6\,\mathrm{nH}$ ,  $C_{line}$ =  $92\,\mathrm{pF}$ 。改进前后的CCD 分别称为 CCD1 和 CCD2,其中 CCD1 的  $R_{hb}$  为  $2.8\,\Omega$ ,  $C_{hb}$  为  $4.8\,\mathrm{nF}$ ; CCD2 的  $R_{hb}$  减小为  $2\,\Omega$ ,  $C_{hb}$  减小为  $4.5\,\mathrm{nF}$ 。为了保证驱动器的性能满足要求,将驱动芯片的 4 路输出并联,使  $R_{drv}$  减小为  $0.9\,\Omega$ 。在上述各种状态下,对相邻两个驱动时钟相位进行仿真,记录 B 点处的  $V_{max}$  和  $V_{cross}$ ,分别表征对驱动时钟的过冲和衰减的影响,结果如表  $1\,\mathrm{fm}$  示。

表 1 B 点驱动时钟信号电压

Tab.1 Signal level of driving clocks at point B

| No. | Status    | $T_L/\text{ns}$ | $V_{ m max}/{ m V}$ | $V_{ m cross}/{ m V}$ |

|-----|-----------|-----------------|---------------------|-----------------------|

| 1   | PCB1-CCD1 | 200             | 9.91                | 8.33                  |

| 2   | PCB1-CCD1 | 300             | 14.1                | 11.81                 |

| 3   | PCB2-CCD1 | 200             | 9.69                | 8.62                  |

| 4   | PCB2-CCD1 | 300             | 9.95                | 9.43                  |

| 5   | PCB2-CCD2 | 100             | 9.88                | 9.11                  |

| 6   | PCB2-CCD2 | 200             | 10.0                | 9.90                  |

从表中可见,相对于 PCB1, PCB2 的驱动时钟过冲得到了明显改善;而 CCD2 相对于 CCD1 也有效减小了驱动时钟的衰减。另外,CCD2 由于内部结构和时序也进行了优化,在同样的行转移时间下,驱动时钟频率减小了一半,即其行转移时间  $T_L$  为 100 ns 时的时钟频率相当于 CCD1 的  $T_L$  为 200 ns 时的时钟频率。

## 3 测试结果与分析

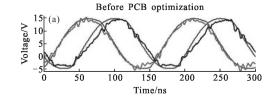

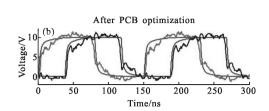

将使用 PCB1 和 PCB2 驱动 CCD1 时 A 点的实测波形与仿真结果进行对比,如图 8 所示。由图可见,仿真与实测结果较为吻合,验证了文中所建立的驱动电路模型的有效性;经优化,PCB2 的驱动时钟过冲和边沿速率均得到了显著改善。

图 8 PCB 优化前后仿真及实测波形对比

Fig.8 Simulated/measured waveforms before/after PCB optimization

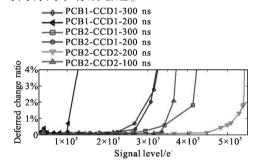

图 9 所示为使用优化前后的 PCB 和 CCD 在不同行转移时间下实测的残余电荷系数  $D_F$  随信号大小变化的趋势。设所允许的  $D_F$  为 2%,对应的信号电子数为满阱电子数,则在优化前后的满阱电子数如表 2 所示。可见,经过优化,满阱电子数得到了显著提高。结合表 1 可知,对于  $V_{\text{cross}}$ ,有 No.6>No.4>No.5>No.3>No.1,这与表 2 的测试结果完全匹配;而对于No.2 的状态,由于  $V_{\text{max}}$  过高,受界面态影响,引起满阱电子数降低。可见,仿真结果与测量结果是一致的。经过 CCD 驱动电路及 CCD 内部结构的优化,在符合满阱电子数和残余电荷系数要求的前提下,行转移时间得到了有效缩短。

图 9 残余电荷系数随信号大小的变化

Fig.9 Deferred charge ratio with different signal levels

表 2 优化前后的满阱电子数

Tab.2 Full well electron number before and after optimization

| No. | Status    | $T_L/\mathrm{ns}$ | Saturation level                    |

|-----|-----------|-------------------|-------------------------------------|

| 1   | PCB1-CCD1 | 200               | 1.12×10 <sup>5</sup> e <sup>-</sup> |

| 2   | PCB1-CCD1 | 300               | $3.08 \times 10^{5} \mathrm{e^{-}}$ |

| 3   | PCB2-CCD1 | 200               | $3.01 \times 10^5 \mathrm{e^-}$     |

| 4   | PCB2-CCD1 | 300               | $4.14 \times 10^{5} \mathrm{e^{-}}$ |

| 5   | PCB2-CCD2 | 100               | $3.64 \times 10^5 \mathrm{e}^-$     |

| 6   | PCB2-CCD2 | 200               | $5.41 \times 10^5 \mathrm{e^-}$     |

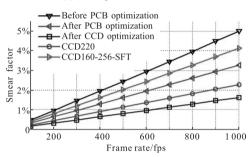

由表 2 可见,要保证 30 万个电子的满阱电子数,则在 PCB 优化前、PCB 优化后和 CCD 优化后所需的最短行转移时间分别为 300 ns、200 ns 和 100 ns。假设前文所述的 CCD160-256-SFT 和 CCD220 以及

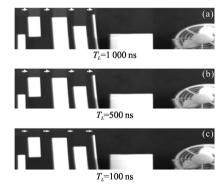

文中优化前后的 CCD 的帧转移行数均为 160 行,则拖尾系数随帧频的变化情况如图 10 所示。从图中可见,文中改进后的 CCD 在 500 fps 的帧频下能实现小于 1% 的拖尾系数,从而使得 CCD 在高帧频应用中仍能保持良好的测量精度。图 11 为在帧频为 500 fps 时不同的行转移时间下对同一场景的成像结果,为加强对比,灰度值经过了拉伸。图中箭头所示位置为白色景物造成的拖尾信号。在  $T_L$  为 1000 ns(科学级 CCD 的较好水平)时,拖尾造成的白色亮条清晰可见,而在  $T_L$  为 100 ns 时,拖尾现象几乎无法察觉,这表明文中实现的 CCD 成像系统在高帧频下仍能保持良好的拖尾抑制效果。

图 10 不同帧频下的拖尾系数

Fig.10 Smear factor with different frame rates

图 11 在 500 fps 下不同  $T_L$  导致的拖尾现象对比 Fig.11 Smear effect with different  $T_L$  @ 500 fps

#### 4 结论

文中通过优化 PCB 设计,并对 CCD 芯片设计提出改进要求,显著缩短了行转移时间,从而大大减小了拖尾引起的误差。所建立的驱动电路模型与传统模型相比,能更准确地预测 CCD 内部和外部的驱动信号波形,为 PCB 的优化提供了指导;同时,发挥了针对高帧频应用进行 CCD 定制的独特优势,使CCD 的拖尾性能达到同类器件的先进水平。在 CMOS

图像传感器综合性能日益提高的今天,文中的工作在一定程度上弥补了 CCD 的缺陷。随着 CCD 在驱动电路和信息采集与处理电路的集成化、电子倍增技术和深耗尽技术等其他方面的突破,CCD 将与 CMOS 图像传感器一起迎来进一步的发展和更广泛的应用,也将为遥感系统综合性能的提高提供有力的保证。

#### 参考文献:

- [1] Gare P, Nelms N, Nowicki Y. Requirements, developments and challenges for CCD and CMOS image sensors for space applica-tions [EB/OL]. (2013–12–16) [2015–05–20]. http://www.imagesensors.org.

- [2] Zhao Yuan, Wang Fei, Zhang Yu, et al. Elimination of smearing in scanner performance real time evaluation device [J]. *Infrared and Laser Engineering*, 2006, 35(S): 508-511. (in Chinese)

- [3] Keith Powell, Deeph Chana, David Fish, et al. Restoration and frequency analysis of smeared CCD images [J]. Applied Optics, 1999, 38(8): 1343–1347.

- [4] Zhang Yu, Wang Wenhua, Li Guoning, et al. Real –time correction method of smear phenomenon based on interline transfer area CCD [J]. *Infrared and Laser Engineering*, 2012, 41(7): 1952–1958. (in Chinese)

- [5] Arai T, Hayashida T, Kitamura K, et al. Development of ultra-high-speed CCD with maximum frame rate of 2 million frames per second[C]//SPIE, 2011, 7934: 79340J.

- [6] Dao V T S, Takeharu G E, Masatoshi T, et al. Toward 100 mega-frames per second: design of an ultimate ultra-high-speed image sensor [EB/OL]. (2009-12-24) [2015-05-20]. http://www.mdpi.com/journal/sensors.

- [7] Wang Yan, He Zhikuan. Design of high –speed driving circuit for large area array full frame transfer CCD [C]// SPIE, 2011, 8194: 819411.

- [8] Guerin D C, Fisher J, Graham E R, et al. The enhanced MODIS airborne simulator hyperspectral imager [C]//SPIE, 2011, 8048: 80480L.

- [9] Feautrier P, Gach J L, Balard P, et al. OCam with CCD220, the fastest and most sensitive camera to date for AO wavefront sensing [J]. *Publications of the Astronomical Society of the Pacific*, 2011, 123(901): 263–274.

- [10] Rubinstein J, Penfield P, Horowitz M A. Signal delay in RC tree networks [J]. *IEEE Transactions on Computer-aided Design*, 1983, CAD-2(3): 202-211.

- [11] Janesick J R. Scientific charge coupled device[C]//SPIE Press Monograph, 2001: 273–300.