# 阵列波导光栅解复用器的偏振相关损耗的优化

孙健1,2,吴远大2,吴卫锋2,单崇新1\*

1郑州大学物理学院,河南郑州 450001;

2河南仕佳光子科技股份有限公司,河南 鹤壁 458030

摘要 对硅基二氧化硅阵列波导光栅解复用器(AWG DEMUX)的偏振相关损耗(PDL)进行了优化。理论分析了引起 AWG 偏振相关性的物理因素以及消除偏振相关性的工艺方法和条件。利用化学气相沉积、光刻和刻蚀等半导体工艺制备了 AWG DEMUX 芯片,并结合理论分析对包层材料中的硼(B)、磷(P)含量进行了优化调整,成功地将芯片的 PDL 降低至 0.12 dB,使 PDL 参数满足芯片的商用化需求。

关键词 光通信;阵列波导光栅;解复用器;偏振相关损耗

中图分类号 TN256

文献标志码 A

doi: 10.3788/CJL202047.0106003

# Optimization of Polarization-Dependent Loss of Arrayed Waveguide Grating Demultiplexer

Sun Jian<sup>1,2</sup>, Wu Yuanda<sup>2</sup>, Wu Weifeng<sup>2</sup>, Shan Chongxin<sup>1\*</sup>

<sup>1</sup>School of Physics, Zhengzhou University, Zhengzhou, Henan 450001, China;

<sup>2</sup> Henan Shijia Photons Technology Co., Ltd., Hebi, Henan 458030, China

Abstract In this work, the polarization-dependent loss (PDL) of a SiO<sub>2</sub>/Si arrayed waveguide demultiplexer (AWG DEMUX) is optimized. The physical factors causing the polarization dependence of the AWG and the process methods and conditions required to eliminate this dependence are analyzed theoretically. AWG DEMUX chips are fabricated by semiconductor processes, such as chemical-vapor deposition, photolithography, and etching. The boron and phosphorus contents in the cladding material are optimized and adjusted according to theoretical analysis. The PDLs of the chips are successfully reduced to 0.12 dB so that the PDL parameters meet the chip's commercialization requirements.

**Key words** optical communications; array waveguide grating; demultiplexer; polarization dependent loss **OCIS codes** 060.4005; 130.3120; 130.3130; 130.5460

## 1 引 言

随着大数据时代的来临,对数据中心之间数据的高速存取和大容量数据传输提出了更高的要求,高速增长的速率和带宽需求将需要更多高速的光收发模块,进而也推动了高速光模块的发展<sup>[1]</sup>。具有20 nm 通道间隔的粗波分复用解复用器(CWDM DEMUX)作为光接收器的核心元件之一,有着广泛的需求和发展空间。

目前,能够实现 CWDM 功能的器件主要有薄膜滤波片和阵列波导光栅(AWG)[2-3]。其中薄膜滤波片具有低插损、高带宽及较大的串扰等优点,但在

模块加工过程中组装工艺复杂,成本较高;而 AWG 不仅可以达到与薄膜滤波片相近的光学性能,同时可以降低组装工艺难度,提高效率,降低成本,因而在目前的光接收器中被广泛使用。制备 AWG 的材料主要包括聚合物、二氧化硅以及磷化铟等材料主要包括聚合物、二氧化硅以及磷化铟等材料。其中二氧化硅具有较低的传输损耗、良好的可靠性,以及与石英光纤能实现较好的匹配等优点,成为制作 AWG 的主要材料。AWG 光学性能参数主要有插入损耗、偏振相关损耗(PDL)、带宽和串扰等,其中 PDL 是衡量 AWG 偏振相关性的主要参数。在 优化 AWG 偏振相关性的方法,通Wildermuth等[6]报道了一种应力释放槽的方法,通

收稿日期: 2019-08-20; 修回日期: 2019-09-15; 录用日期: 2019-09-26

\* E-mail: cxshan@sohu.com

过在阵列波导处刻蚀应力释放槽,有效地改善了AWG的偏振相关性,但是这种方法增加了工艺难度,不利于批量生产;Lu等<sup>[7]</sup>在AWG输入端引入了一个偏振控制器,可以使进入AWG的随机偏振光转化为同TE。模偏振方向相同的线偏振光,但是这种设计要求输入波导的厚度较薄,增加了波导与光纤的耦合损耗。而对于通过AWG包层应力调控来改善偏振相关性的方法,其工艺难度较低,有利于批量生产,安俊明等<sup>[8]</sup>和 de Peralta等<sup>[9]</sup>在这方面都进行过理论分析。

本文主要对硅基二氧化硅 AWG DEMUX 芯片的 PDL 参数进行工艺优化。利用化学气相沉积(CVD)、光刻和刻蚀等半导体工艺制备了四通道的AWG DEMUX 芯片,波长间隔为 20 nm;依据理论指导对上包层材料中的硼(B)、磷(P)掺杂含量进行调整,有效地降低了 PDL,使其满足商用芯片的参数标准。

#### 2 AWG 偏振相关性原理

对于硅基二氧化硅型 AWG,不同偏振态下 AWG 波导的波长偏移为

$$\Delta \lambda = |\lambda_{\rm TM} - \lambda_{\rm TE}| = B(\Delta L/m), \qquad (1)$$

$$B = n_{\text{TE}} - n_{\text{TM}}, \qquad (2)$$

式中:λ<sub>TM</sub>和λ<sub>TE</sub>分别为 TM 和 TE 两种偏振态下的 中心波长;B 为双折射系数;m 为 AWG 的衍射级 数; $\Delta L$  为相邻阵列波导间的长度差; $n_{\text{TE}}$ 和  $n_{\text{TM}}$ 分别 为 TE 和 TM 两种偏振态下二氧化硅的折射率。 AWG 在不同偏振态下的波长存在偏移,形成不同 偏振态下的光谱波形分离,从而表现出显著的偏振 相关性。根据(1)式可知,想要消除 AWG 波导的偏 振相关性,就要使波导的双折射系数 B 减小。而使 波导存在较大双折射系数的原因是二氧化硅波导材 料与硅衬底材料的热膨胀系数不同,致使高温处理 后的波导在两个垂直方向上受到大小不同的应力, 从而使波导具有较高的双折射系数。硅衬底的热膨 胀系数比二氧化硅的热膨胀系数大一个数量级左 右,因此本文通过增大二氧化硅包层生长气体中 B<sub>2</sub>H<sub>6</sub>和PH<sub>3</sub>的含量,来提高二氧化硅的热膨胀系 数,从而消除或减小波导的双折射。

#### 3 芯片制备及测试

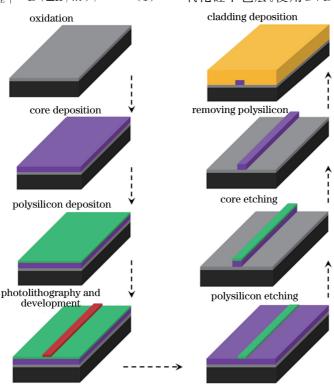

图 1 是芯片的制备工艺流程示意图。首先,通过湿法氧化工艺在硅衬底表面形成 15 μm 厚的氧化硅下包层。使用CVD设备在下包层表面沉积一

图 1 AWG 芯片的制备工艺流程

Fig. 1 Fabrication process of AWG chip

层高折射率的二氧化硅芯层,反应气体是  $SiH_4$ 和  $N_2O$ ,掺杂气体为  $GeH_4$ ;沉积芯层后,晶圆在 1100  $^{\circ}$ 条件下退火 8 h,然后在芯区表面沉积硬掩模层。通过光刻、显影工艺,在硬掩模层表面制备 光刻胶掩模;通过对硬掩模进行干法刻蚀,将光刻 胶图形转移到硬掩模层上;然后,去掉光刻胶,对 芯区的二氧化硅层进行干法刻蚀,形成芯区波导

(a) 2 μm

图形;最后,去掉芯区波导上的硬掩模层,通过 CVD沉积B、P掺杂的二氧化硅包层,并对晶圆进 行高温回流。

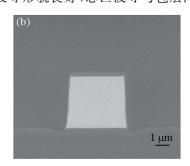

图 2(a)是芯区刻蚀后通过激光共聚焦显微镜测量到的波导形貌照片,图 2(b)是沉积上包层后的波导端面 SEM 照片,波导尺寸为  $4.5~\mu m \times 4.5~\mu m$ ,波导形貌良好,芯区波导与包层间界面清晰。

图 2 矩形波导的形貌照片。(a)光学显微镜照片;(b) SEM 照片

Fig. 2 Morphology photos of rectangular waveguide. (a) Optical microscope photograph; (b) SEM image

对于硅基二氧化硅型 AWG,增加二氧化硅包层中B或P的含量,可以提高二氧化硅的热膨胀系数。但是实验中发现:随着B含量的增加,包层的折射率会逐渐降低;而随着P含量增加,包层的折射率会逐渐变大。单独改变包层中B或P的含量,无法使上包层折射率满足设计需求。因此,实验中同时调整包层生长气体中的 $B_2H_6$ 和 $PH_3$ 流量,在保持包层折射率稳定的前提下优化 AWG 的PDL。

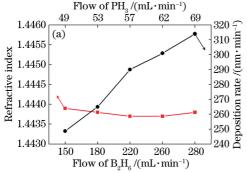

对于不同  $B_2$   $H_6$  和  $PH_3$  掺杂的二氧化硅薄膜,采用棱镜耦合仪和膜厚仪分别对以上薄膜的折射率和沉积速率进行表征。如图 3(a) 所示, $B_2$   $H_6$  /  $PH_3$  气体流量从150  $mL \cdot min^{-1}/49$   $mL \cdot min^{-1}$  逐渐增加到  $280 \ mL \cdot min^{-1}/69 \ mL \cdot min^{-1}$ ,薄膜的沉积速率从  $247 \ nm/min$  逐渐增大到  $313.25 \ nm/min$ ,而折射率基本保持在 1.4438 附近。

当薄膜沉积在硅衬底上时,应力的作用会使衬底发生弯曲,通过对弯曲量的测量就可以获得薄膜应力的大小。本文采用应力测试仪对薄膜应力进行表征,应力表示为

$$\sigma = \frac{Eh^2}{(1-v)6Rt},\tag{3}$$

$$\frac{1}{R} = \frac{1}{R_2} - \frac{1}{R_1},\tag{4}$$

式中:E 为衬底的杨氏模量;v 为泊松比;h 为衬底厚度;t 为薄膜厚度;R 为有效曲率半径 $R_1$  和  $R_2$  分别为薄膜沉积前后衬底的曲率半径。通过测量薄膜沉积前后衬底曲率半径,就可以获得薄膜应力的大小。薄膜的应力随  $B_2H_6/PH_3$  气体流量的变化曲线如图 3(b)所示,当  $B_2H_6/PH_3$  气体流量为 150  $mL \cdot min^{-1}$  村,应 力 为

图 3 薄膜特性与气体流量之间的关系。(a)薄膜折射率和沉积速率与  $B_2H_6/PH_3$  气体流量的关系;(b)薄膜应力与  $B_2H_6/PH_3$  气体流量的关系

Fig. 3 Relation between film properties and gas flow. (a) Refractive index of film and deposition rate versus gas flow of  $B_2 H_6/PH_3$ ; (b) relation between film stress and gas flow of  $B_2 H_6/PH_3$

—90 MPa;随着 B<sub>2</sub>H<sub>6</sub> 和 PH<sub>3</sub>流量的增加,应力逐渐 变 小; 当 B<sub>2</sub>H<sub>6</sub>/PH<sub>3</sub> 气 体 流 量 达 到 280 mL·min<sup>-1</sup>/69 mL·min<sup>-1</sup> 时,应力降低到—20 MPa。

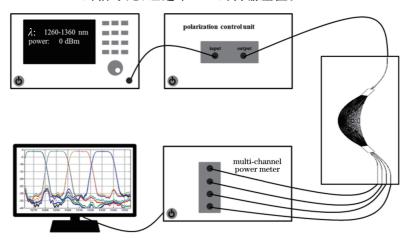

芯片光学测试系统如图 4 所示。可调谐激光器输出波长范围为 1260~1360 nm 的信号光,经过单

模光纤连接到偏振控制单元,并通过单模光纤耦合进入芯片的输入端。芯片输出端通过单模光纤连接到光功率计,将光信号转换成电信号,并在计算机上显示芯片的测试光谱。偏振控制单元对光信号的偏振态进行扫描,PDL是光芯片在不同偏振态下最大的传输差值。

图 4 芯片测试系统示意图

Fig. 4 Diagram of testing system of chip

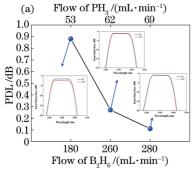

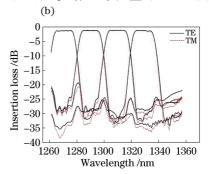

芯片的 PDL 随  $B_2H_6/PH_3$  气体流量的变化曲线如图 5(a)所示。从图中数据可以看出,在  $B_2H_6/PH_3$  流量为  $180~mL \cdot min^{-1}/53~mL \cdot min^{-1}$  时, TE 和 TM 两种偏振态下的波形明显分离,对应的 PDL 参数 达到 0.9~dB; 当  $B_2H_6/PH_3$  流量增大到  $260~mL \cdot min^{-1}/62~mL \cdot min^{-1}$  ,光谱中 TE 和 TM 两种偏振态下的波形趋于重合, PDL 参数降低到 0.25~dB; 当  $B_2H_6/PH_3$  流量增大到  $280~mL \cdot min^{-1}/69~mL \cdot min^{-1}$ , PDL 参数继续降低到 0.12~dB, 芯片的输出光谱如图 5(b)所示,可以看出四个通道的光谱波形都重合得较好,说明通道间的 PDL 具有良好的一致性,完全满足商用 AWG DEMUX 芯片对

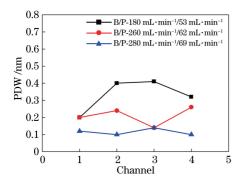

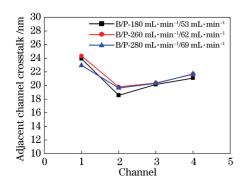

PDL 参数的要求。芯片四个输出信道的偏振相关 波长(PDW)随  $B_2H_6/PH_3$  气体流量的变化曲线如图 6 所示。从图中可以看出,PDW 同样随着  $B_2H_6/PH_3$  气体流量的增大而逐渐变小。芯片的相邻串 扰随  $B_2H_6/PH_3$  气体流量的变化曲线如图 7 所示。从图中可以看出, $B_2H_6/PH_3$  气体流量的变化对串 扰的影响并不明显。

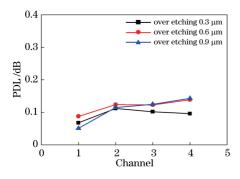

除了研究 B<sub>2</sub> H<sub>6</sub>/PH<sub>3</sub> 流量对 PDL 的影响外,本 文针对波导过刻蚀深度对 PDL 的影响进行了实验研 究。波导过刻蚀深度与 PDL 的关系如图 8 所示,可 以看出,波导过刻蚀深度的变化对 PDL 影响并不明 显,没有 B<sub>2</sub> H<sub>6</sub>/PH<sub>3</sub> 流量对 PDL 的影响显著。

图 5 芯片的偏振特性与气体流量之间的关系。(a) PDL 和传输光谱与气体流量的关系; (b)上包层高掺杂条件下 AWG 的输出光谱

Fig. 5 Relation between polarization characteristics of chip and gas flow. (a) PDL and transmission spectrum versus gas flow; (b) output spectra of AWG with high doped cladding

图 6 芯片 PDW 与 B<sub>2</sub> H<sub>6</sub>/PH<sub>3</sub> 流量的关系曲线 Fig. 6 Relation between PDW of chip and gas flow of B<sub>2</sub> H<sub>6</sub>/PH<sub>3</sub>

图 7 相邻串扰与  $B_2$   $H_6/PH_3$  流量的关系曲线 Fig. 7 Relation between adjacent channel crosstalk and gas flow of  $B_2$   $H_6/PH_3$

图 8 芯片 PDL 与过刻蚀深度的关系曲线

Fig. 8 Relation between PDL of chip and over

etching depth

## 4 结 论

本文制备了硅基二氧化硅 AWG DEMUX 芯片,主要通过上包层材料中B、P含量的调整和优化,实现对芯片 PDL 参数的优化。实验中对不同B、P 掺杂条件下薄膜的折射率和应力进行了测量,结果表明,提高上包层材料中的B、P含量可以明显

减小薄膜应力。芯片的测试结果显示,在上包层材料中的 B、P 高掺条件下,芯片的 PDL 可以降低到 0.12 dB,完全满足商用芯片对 PDL 参数的要求。

#### 参考文献

- [1] Pan P, An J M, Wang Y, et al. Compact 4-channel AWGs for CWDM and LAN WDM in data center monolithic applications [J]. Optics & Laser Technology, 2015, 75: 177-181.

- [2] Hassan K, Khalil D, Malak M, et al. Design of an arrayed waveguide grating optical demultiplexer for CWDM applications [J]. Journal of Optics A: Pure and Applied Optics, 2008, 10(7): 075307.

- [3] Tangdiongga G E, Lim T G, Li J, et al. Optical design of 4-channel TOSA/ROSA for CWDM applications [J]. Proceedings of SPIE, 2008, 6899: 68990L

- [4] Juhari N, Menon P S, Ehsan A A, et al. 4-channel double S-shaped AWG demultiplexer on SOI for CWDM[C] // 2015 17th International Conference on Advanced Communication Technology (ICACT), July 1-3, 2015, Seoul, Korea. New York: IEEE, 2015: 436-440.

- [5] Yurt N, Rausch K, Kost A R, et al. Design and fabrication of a broadband polarization and temperature insensitive arrayed waveguide grating on InP[J]. Optics Express, 2005, 13(14): 5535-5541.

- [6] Wildermuth E, Nadler C, Lanker M, et al. Penalty-free polarisation compensation of SiO<sub>2</sub>/Si arrayed waveguide grating wavelength multiplexers using stress release grooves[J]. Electronics Letters, 1998, 34(17): 1661-1662.

- [7] Lu P, Liu D M, Chen J, et al. Novel polarizationinsensitive arrayed-waveguide grating multiplexer design [J]. Proceedings of SPIE, 2002, 4904: 495-499.

- [8] An J M, Ban S L, Liang X X, et al. Numerical analysis for a SiO<sub>2</sub>/Si waveguide stress-birefringence [J]. Chinese Journal of Semiconductors, 2005, 26 (7): 1454-1458.

安俊明, 班士良, 梁希侠, 等. SiO<sub>2</sub>/Si 波导应力双 折射数值分析[J]. 半导体学报, 2005, 26(7): 1454-

- [9] de Peralta L G, Bernussi A A, Temkin H, et al. Silicon-dioxide waveguides with low birefringence[J]. IEEE Journal of Quantum Electronics, 2003, 39(7): 874-879.

1458.