# 单片集成 430 GHz 三倍频器的设计及测试

杨大宝1, 邢东1,2, 梁士雄1,2\*\*, 张立森1,2, 徐鹏1, 冯志红1,2\*

1中国电子科技集团公司第十三研究所,河北 石家庄 050051;

2专用集成电路国家级重点实验室,河北 石家庄 050051

摘要 通过单片集成的方法,将工作于太赫兹频段(430 GHz)的三倍频器的各个功能电路集成在厚度为  $12~\mu m$  的 砷化镓薄膜单片上,设计、制造太赫兹三倍频集成电路单片。单片结构采用一对反向并联连接的肖特基二极管,构成串联平衡式电路,电路不需要外加偏置电压。平衡式电路只产生奇数次谐波,简化了电路分析和优化过程。电路设计采用三维电磁仿真软件与谐波非线性仿真软件联合仿真场路的方法,准确模拟单片电路的射频特性。将单片电路安装在中间剖开的波导腔体内制成三倍频器进行测试,在 430 GHz 处测得输出功率为  $215.7~\mu W$ ,效率为 4.3%。

关键词 太赫兹技术;三倍频;反向并联;单片集成;肖特基势垒二极管

中图分类号 TN454

文献标识码 A

doi: 10.3788/CJL201946.0614035

## Design and Test of Monolithically Integrated 430 GHz Frequency Tripler

Yang Dabao<sup>1</sup>, Xing Dong<sup>1,2</sup>, Liang Shixiong<sup>1,2\*\*</sup>, Zhang Lisen<sup>1,2</sup>, Xu Peng<sup>1</sup>, Feng Zhihong<sup>1,2\*</sup>

<sup>1</sup> The 13<sup>th</sup> Research Institute of China Electronics Technology Group Corporation, Shijiazhuang, Hebei 050051, China;

<sup>2</sup> National Key Laboratory of Application Specific Integrated Circuit (ASIC), Shijiazhuang, Hebei 050051, China

Abstract A 430 GHz tripler circuit in the terahertz range, which consists of all parts of a tripler, has been designed and fabricated on a 12  $\mu$ m thick GaAs film substrate. A pair of two matched anti-parallel Schottky diodes without application of direct current bias is used to realize series balanced tripler structure. One distinct advantage of the balanced configuration is that it generates only odd harmonics, which simplifies the tripler analysis and optimization. Harmonic nonlinear simulations and three-dimensional electromagnetic simulations are combined to simulate radio-frequency performance of the entire tripler circuit accurately. The monolithically integrated 430 GHz tripler circuit is mounted in a split waveguide block for test. It has produced a peak output power of 215.7  $\mu$ W with 4.3% efficiency at 430 GHz.

**Key words** terahertz technology; frequency tripling; anti-parallel connection; monolithic integration; Schottky barrier diodes

OCIS codes 190.2620; 190.4223

# 1 引 言

太赫兹(THz) 频段的信号具有频率高、安全性好、穿透性好的优点,在电子、信息、安防、生命科学、国防、航天等领域具有广阔的应用前景。尤其在最近几十年,随着半导体工艺技术的提高,太赫兹频段的应用技术得到越来越广泛的关注[1]。平面肖特基二极管技术近二十年来开始被使用并得到迅速发

展<sup>[2-3]</sup>,现在已经逐渐取代触须式二极管在太赫兹波 段得到巨大发展和广泛应用。

早在 2001 年,Bruston 等  $^{[4]}$  报道了一种基于平面肖特基二极管的 1.2 THz 三倍频器,此三倍频器基于平衡式结构,以反向并联二极管对为核心器件,能够较好地抑制偶次能量,改善变频效率。测试表明温度为 50 K 时,输出功率可达 250  $\mu$ W。 2005年,Maestrini 等  $^{[5]}$  基于单片电路研制了一个 540  $^{\sim}$

收稿日期: 2019-01-24; 修回日期: 2019-04-16; 录用日期: 2019-05-06

<sup>\*</sup> **E-mail**: Ga917vv@163.com; \*\* **E-mail**: wialliam@163.com

640 GHz 的平衡式三倍频器,该三倍频器的整个悬置微带电路安装在波导模块中一个 12 μm 厚的支架上,二极管单元一端的梁式引线同时提供射频/直流接地。在常温条件下,输出功率能够达到 0.9~1.8 mW,倍频效率为 4.5%~9.0%;当温度下降至120 K时,三倍频器可以输出 2.0~4.2 mW 的功率,此时倍频效率为 8%~12%。2007 年,Porterfield等<sup>[6]</sup>报道了 220 GHz 和 440 GHz 高效三倍频器。倍频电路采用四管芯变容二极管构成同向并联结构,将二次谐波能量反射并再利用,提高三倍频器的输出功率,此结构便于偏置电压的加载。测试结果显示,220 GHz 三倍频器输出功率可达 23 mW,效率可达 16%。440 GHz 三倍频器输出功率可达 13 mW,效率可达 12%。

2011 年,Li 等[7]提出了基于硅基工艺的900 GHz 宽带 三倍 频器。室温下,该三倍频器在828~963 GHz 的频带范围内输出功率大于60  $\mu$ W,其中在909 GHz 处具有最大85.3  $\mu$ W 的输出功率。2015 年,Wang 等[8]报道了一个用于多普勒气象雷达的280 GHz 三倍频器,由六只肖特基二极管同向串联集成在AlN基片上,这种平衡结构可以抑制偶次谐波。测试结果表明,驱动功率为100 mW 时,在240~290 GHz 内倍 频 效率为1%~5%,输出功率在276 GHz处达到最大值,为15 mW,效率为5%。

由于半导体制造技术的限制,国内太赫兹倍频技术发展相对落后。2014年,张勇等[3]利用 UMS公司的肖特基变容管设计了一个 220 GHz 的三倍频器,频段内最大输出功率为 1.7 mW,倍频效率大于 0.56%。2015年, Ren 等[10]报 道了 330~

500 GHz 零偏置单片集成宽带三倍频器,高电子迁移率 InGaAs 肖特基二极管集成在 InP 基板上;输入功率为  $9\sim10$  mW 时,倍频器在  $330\sim500$  GHz 频段内输出功率大于 $10~\mu$ W,倍频效率最高达 2%。 2015 年,韩祎炜[11] 研究了基于 GaAs 单片集成的 650 GHz三倍频器,其基板厚度为  $12~\mu$ m,在  $633\sim652$  GHz 频段内输出功率超过  $0.02~\mu$ W,646.6 GHz 处达到峰值,约为  $0.086~\mu$ M,对应倍频效率约 0.5%。

在太赫兹频段固态功能模块装配中,需要进行将平面肖特基二极管倒装焊安装到基片电路并将基片电路安装到波导腔体内的工艺操作,这些操作引起的不可控误差影响随着工作频率的提升而急剧提高<sup>[12]</sup>。消除这些误差的手段主要是降低操作难度和简化操作过程,将非线性器件和外围匹配电路制成太赫兹单片集成电路(TMIC)后再进行模块安装是实现这一目标的重要手段。现阶段,TMIC技术已经成为太赫兹频段电路设计应用的主流趋势,国外太赫兹电路单片集成化技术已经取得较大进展<sup>[13]</sup>,国内也开始了相关探索性研究,本文将介绍本课题组在TMIC方面取得的进展。

## 2 太赫兹三倍频器集成电路设计

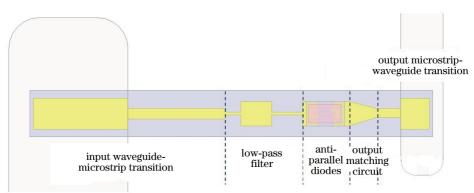

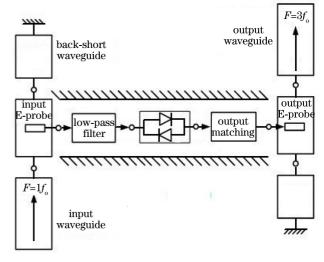

太赫兹三倍频器集成电路采用反向并联结构的 肖特基二极管,串联接在输入和输出匹配电路中间, 采用串联平衡式电路结构,如图 1 和图 2 所示。这 种电路具有结构简单、倍频效率较高的特点,可稳定 工作于整个毫米波及亚毫米波频段,非常适于高性 能太赫兹系统。

图 1 三倍频器平面电路示意图

Fig. 1 Schematic of frequency tripler planar circuit

太赫兹频段的信号波长与二极管结构尺寸相近, 因此在仿真设计时必须按照分布元件予以考虑。为 了便于电路的整体仿真,将电路按功能分成几个独立 的部分,利用三维电磁仿真软件对每个单元进行单独 仿真形成各个功能单元参数包后,再代入谐波平衡非 线性软件中与二极管场路相结合进行整体仿真优化。

图 2 整体电路示意图

Fig. 2 Block diagram of the whole circuit

## 2.1 肖特基二极管建模

单片上的二极管部分决定了电路工作的上限,因此设计单片电路时首先考虑二极管工作频率的上限。二极管频率特性主要由其特有的截止频率 f。决定,f。计算公式为 f。=1/[2 $\pi R$ <sub>s</sub>(C<sub>j</sub>0+C<sub>p</sub>)](R<sub>s</sub>为二极管串联电阻;C<sub>j</sub>0为零偏压结电容;C<sub>p</sub>为管壳的寄生电容)。集成在单片上的肖特基二极管用传统方式设计,阴极为欧姆接触,阳极为肖特基接触。

为保证芯片在太赫兹频段能正常工作,在现有工艺条件下,设计中主要通过砷化镓(GaAs)基片减薄和点支撑的空气桥结构工艺降低二极管外围电路的寄生电容  $C_p$ ,使二极管达到太赫兹频段工作要求。单片电路采用平面肖特基二极管,按照本课题组自主研制成功的太赫兹单管设计,单阳极二极管参数如表1所示(n 为发射系数; $I_s$  为饱和电流; $V_f$  为反向击穿电压)。

表 1 平面肖特基二极管的参数

Table 1 Planar Schottky diode parameters

| Parameter | $R_{	ext{s}}/\Omega$ | n   | $I_s/fA$ | $V_{ m f}/{ m V}$ | $C_{\rm j0}/{ m fF}$ | $C_{\scriptscriptstyle \mathrm{p}}/\mathrm{fF}$ | $f_{\rm c}/{ m THz}$ |

|-----------|----------------------|-----|----------|-------------------|----------------------|-------------------------------------------------|----------------------|

| Value     | 4                    | 1.2 | 50       | 0.6               | 3                    | 4                                               | 5.7                  |

二极管的  $C_{j0}$  为 3 fF,而总电容  $C_{j0}$  +  $C_{p}$  为 7 fF;申联电阻  $R_{s}$  为 4  $\Omega$ ,计算得出截止频率  $f_{c}$  为 5.7 THz。在工程应用中,当工作频率低于截止频率的 1/10 时能正常工作,因此芯片中的二极管能保证满足上限为 570 GHz 频率的应用。

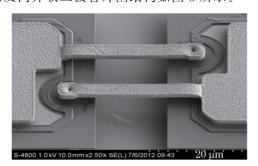

二极管的准确建模是单片电路整体优化的基础,在建模仿真中必须充分考虑二极管的外围结构和材料影响。首先需要按照二极管外围结构的电场分布进行建模仿真,集成在 12 μm 厚的 GaAs 基片上的反向并联二极管外围结构如图 3 所示。

图 3 反向并联二极管芯片

Fig. 3 Drawing of anti-parallel diode chip

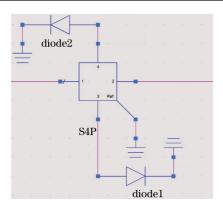

按照图 3 所示二极管的结构和材料构成,用三维电磁仿真软件建立反向并联二极管参数模型后,计算得到模型端口 S 参数(散射参量)包 S4P,与非线性仿真软件自带的二极管 SPICE 模型 diode1 和diode2(按二极管的静态特性参数设定)相结合级联,这样场路结合处理充分考虑了二极管肖特基结的工作机理及其半导体层结构的影响,构成在太赫兹频段应用的二极管的完整准确的模型。图 4 所示为三倍频二极管的三维物理结构电场建模和非线性仿真电路模型。

#### 2.2 太赫兹三倍频器的设计

### 2.2.1 三倍频器的建模设计

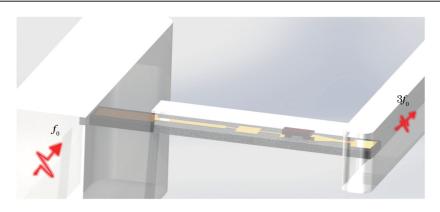

三倍频器采用传统的二等分波导腔体结构设计:单片固定到横跨基波输入波导和三倍频输出腔体 E 面腔中部的微带腔槽内,基频输入和三倍频输出的波导腔具有固定短路面。

图 5 所示为三倍频器拓扑结构(F 为波导腔体内的工作频率)。电路采用串联平衡式结构。频率为 f。的基波射频信号通过肖特基反向并联二极管对时,通过二极管的非线性效应生成各次谐波倍频

图 4 二极管的结构仿真和模型

Fig. 4 Simulated structure and model of diode

分量,鉴于串联平衡式电路结构本身固有的性质,电路只有奇次倍频项输出,幅度为单管的两倍。因此三倍频单片电路输入设计主要保证基波功率输入二极管对,输出设计只需要对三次谐波倍频的频率(3f。)匹配电路即可,输出电路中不存在基波的偶次倍频项,免去谐波回收用以提高倍频效率的电路设计,简化了电路设计。

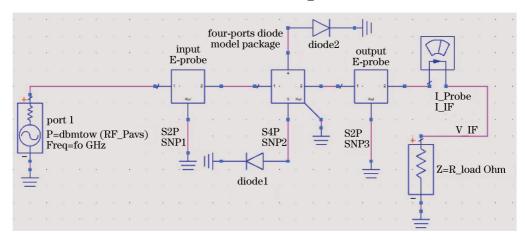

#### 2.2.2 三倍频单片集成电路的整体仿真

三倍频电路中的反向并联二极管对和电路其他 部分集成在 12 μm 厚的 GaAs 薄膜上。在非线性电

图 5 三倍频器的电路拓扑结构

Fig. 5 Circuit topology of the tripler

路整体优化仿真设计中,微带基片需要定义材料为 GaAs,厚度定义为  $12~\mu m$ ,三倍频单片的整体仿真 模型如图 6~m示(port 1~b输入基波源信号,P~b输入功率,Freq~b输入频率,S2P、S4P 代表 2~m口和 4~m口数据包,SNP1、SNP2、SNP3 分别为输入 E~m探针、二极管外围结构、输出 E~m探针数据包, $I_IF~m~V~IF~b$ 输出负载 Z~m的电流和电压)。

图 6 三倍频电路的整体仿真模型

Fig. 6 Integrated simulation model of the tripler circuit

三倍频单片集成电路必须与所在波导腔体进行整体仿真,固定短路面输入和输出波导腔体实现波导与微带电路的功率转换,必须充分考虑电路设计的重要组成部分。电路整体仿真前,首先对倍频电路各个组成部分分别用三维电磁仿真软件进行电磁场的仿真优化,生成非线性电路分析软件可识别的 S 参数包;其次,将二极管外围结构场分析参数包与二极管 SPICE 参数模型级联,构成充分考虑二极管外围结构对电场影响的完整二极管模型;最后,加载

电路其他组成部分场分析参数包,用谐波平衡分析 法对电路整体进行非线性仿真优化。

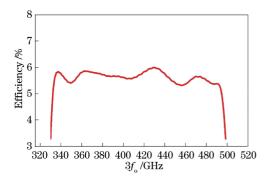

电路设计中,优化目标是在宽频带中实现最高倍频效率。将基波输入功率定义为 5 mW 时,电路整体效率优化结果如图 7 所示,横轴为输出频率 3 f。(f。为基波输入频率),在三倍频输出频率为 430 GHz(对应基波输入为 143.3 GHz)时的仿真效率为 5.988%。

二极管结电容  $C_{io}$  和串联电阻  $R_{s}$  对倍频模块

图 7 三倍频电路效率的仿真结果

Fig. 7 Simulated efficiency of tripler circuit

效率会有影响。一般情况下,结电容和串联电阻与 效率成反比,结电容和串联电阻越小,效率越高。然 而,结电容与串联电阻在工艺制作中互相牵制,结电 容大则串联电阻小,结电容小则串联电阻大。计算 仿真表明,结电容对效率的影响比串联电阻大得多, 因此在单片制作中优先保证结电容指标。

## 3 单片电路加工和测试结果

太赫兹单片集成电路技术对半导体电路的设计和加工技术提出了更高的要求,不仅要求设计准确,同时要求加工精准,这样才能保证集成电路在太赫兹频段具有良好的性能。单片电路在本实验室进行工艺制作和装配。相对于相同频段通过倒装焊工艺将二极管安装到基片电路上再安装到波导腔体的模块装配,单片电路装配相对简单,只需要将单片按定位标记用导电胶粘在波导腔体内即可,降低了装配误差对太赫兹频段的影响。

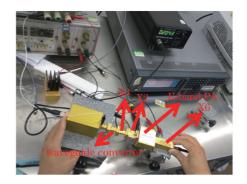

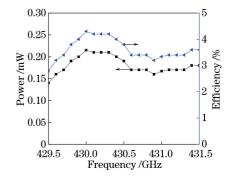

图 8 所示为研制的三倍频单片电路模块测试平台照片。测试时,信号源产生 Ku 波段信号通过六倍频到 E 波段,E 波段信号放大后推动后面二倍频信号生成 D 波段信号,用 D 波段信号推动研制的三倍频器,从而对 430 GHz 的功率输出进行测试。将基波输入频率的功率固定为 5 mW 时,430 GHz 三倍频器测试结果如图 9 所示。

在 430 GHz 频率处,基于单片集成电路的太赫兹三倍频模块输出功率为 215.7 μW,效率为 4.3%。测试结果与仿真结果相比效率有所下降,分析原因如下:1)盒体加工和芯片制造误差;2)建模缺陷和非线性计算不完整性导致的仿真计算误差。此外,三倍频单片电路设计为宽带电路,由于测试手段限制,只测试了带内一小段频率的性能;电路在相关单位进行宽带应用时,满足使用要求,间接验证了单片电路的宽带性能已达到同时代国际先进水平。

图 8 三倍频器测试平台

Fig. 8 Frequency tripler test platform

图 9 430 GHz 三倍频器输出功率和效率

Fig. 9 Measured output power and efficiency of the 430 GHz tripler

# 4 结 论

实验测试结果与设计结果基本符合,这表明场路结合对太赫兹电路仿真设计的有效性。三倍频单片集成电路的研制使用,简化了太赫兹模块的装配工艺,省去将极微小的二极管芯片倒装焊安装到石英基片的工艺环节,使模块安装更为简易。设计成功的三倍频单片电路已经开始小批量应用到用户的产品中,验证了单片电路的可靠性和实用性,其性能指标是已知国内报道的最高水平,与国外同类产品性能相当,推动了国内太赫兹集成电路的发展。此外,这项技术可以应用于亚毫米波的其他频段电路中,使高性能、造价低和可靠性高的亚毫米波功能模块的制造成为可能。

## 参 考 文 献

- [1] Zheng X, Liu C. Recent development of THz technology and its application in radar and communication system (I) [J]. Journal of Microwaves, 2010, 26(6): 1-6.

- 郑新, 刘超. 太赫兹技术的发展及在雷达和通讯系统中的应用(I)[J]. 微波学报, 2010, 26(6): 1-6.

- [2] Bishop W L, McKinney K, Mattauch R J, et al. A

$\lceil 11 \rceil$

- novel whiskerless Schottky diode for millimeter and submillimeter wave application [C] // 1987 IEEE MTT-S International Microwave Symposium Digest, May 9-June 11, 1987, Palo Alto, CA, USA. New York: IEEE, 1987: 607-610.

- [3] Archer J W, Batchelor R A, Smith C J. Low-parasitic, planar Schottky diodes for millimeter-wave integrated circuits [J]. IEEE Transactions on Microwave Theory and Techniques, 1990, 38(1): 15-22.

- [4] Bruston J, Maestrini A, Pukala D, et al. A 1.2 THz planar tripler using GaAs membrane based chips [C]//Proceedings of the Twelfth International Symposium on Space Terahertz Technology, February 14-16, 2001, Shelter Island, San Diego, CA, USA. ADS, 2001: 310-319.

- [5] Maestrini A, Ward J S, Gill J J, et al. A 540-640-GHz high-efficiency four-anode frequency tripler [J]. IEEE Transactions on Microwave Theory and Techniques, 2005, 53(9): 2835-2843.

- [6] Porterfield D.W. High-efficiency terahertz frequency triplers [C] // 2007 IEEE/MTT-S International Microwave Symposium, June 3-8, 2007, Honolulu, HI, USA. New York: IEEE, 2007: 337-340.

- [7] Li Y, Mehdi I, Maestrini A, et al. A broadband 900-GHz silicon micromachined two-anode frequency tripler[J]. IEEE Transactions on Microwave Theory and Techniques, 2011, 59(6): 1673-1681.

- [8] Wang H, Pardo D, Merritt M, et al. 280 GHz frequency multiplied source for meteorological

- Doppler radar applications [C] // 2015 8th UK, Europe, China Millimeter Waves and THz Technology Workshop (UCMMT), September 14-15, 2015, Cardiff, United Kingdom. New York: IEEE, 2015: 2835-2843.

- [9] Zhang Y, Lu Q Q, Liu W, et al. Design of a 220 GHz frequency tripler based on EM model of Schottky diodes [J]. Journal of Infrared and Millimeter Waves, 2014, 33(4): 405-411. 张勇, 卢秋全, 刘伟, 等. 基于肖特基势垒二极管三维电磁模型的 220 GHz 三倍频器[J]. 红外与毫米波学报, 2014, 33(4): 405-411.

- [10] Ren T H, Zhang Y, Yan B, et al. A 330-500 GHz zero-biased broadband tripler based on terahertz monolithic integrated circuits [J]. Chinese Physics Letters, 2015, 32(2): 020702.

Han Y W. The research of GaAs monolithic

- integrated 650 GHz frequency tripler[D]. Chengdu: University of Electronic Science and Technology of China, 2015. 韩祎炜. GaAs 单片集成 650 GHz 三倍频器研究[D]. 成都: 电子科技大学, 2015.

- [12] Hesler J L. Planar Schottky diodes in submillimeterwavelength waveguide receivers [D]. Charlottesville: University of Virginia, 1996.

- [13] Albrecht J D, Rosker M J, Wallace H B, et al. THz electronics projects at DARPA: transistors, TMICs, and amplifiers [C] // 2010 IEEE MTT-S International Microwave Symposium, May 23-28, 2010, Anaheim, CA, USA. 2010: 1118-1121.